KEVIN EDUARDO LUCAS MARCILLO

DM: 21/2018

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil 2018

PERFORMANCE EVALUATION OF ROBUST PARAMETRIC CONTROL STRATEGIES APPLIED ON SUPPRESSION OF OSCILLATIONS EFFECTS DUE TO CONSTANT POWER LOADS IN MULTI-CONVERTER BUCK-BUCK SYSTEMS

KEVIN EDUARDO LUCAS MARCILLO

DM: 21/2018

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil 2018

PERFORMANCE EVALUATION OF ROBUST PARAMETRIC CONTROL STRATEGIES APPLIED ON SUPPRESSION OF OSCILLATIONS EFFECTS DUE TO CONSTANT POWER LOADS IN MULTI-CONVERTER BUCK-BUCK SYSTEMS

Dissertação submetida à banca examinadora do programa de Pós-Graduação em Engenharia Elétrica da UFPA para obtenção do Grau de mestre em Engenharia Elétrica na área de Sistemas de Energia

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil 2018

PERFORMANCE EVALUATION OF ROBUST PARAMETRIC CONTROL STRATEGIES APPLIED ON SUPPRESSION OF OSCILLATIONS EFFECTS DUE TO CONSTANT POWER LOADS IN MULTI-CONVERTER BUCK-BUCK SYSTEMS

DISSERTAÇÃO DE MESTRADO SUBMETIDA À AVALIAÇÃO DA BANCA EXAMINADORA APROVADA PELO COLEGIADO DO PROGRAMA DE PÓSGRADUAÇÃO EM ENGENHARIA ELÉTRICA DA UNIVERSIDADE FEDERAL DO PARÁ E JULGADA ADEQUADA PARA OBTENÇÃO DO GRAU DE MESTRE EM ENGENHARIA ELÉTRICA NA ÁREA DE SISTEMAS DE ENERGIA.

AUTOR: KEVIN EDUARDO LUCAS MARCILLO

**VISTO**

APROVADA EM: 11/06/2018

BANCA EXAMINADORA:

Prof. Dr. Walter Barra Junior (Orientador – PPGEE/UFPA)

Prof. Dr. Marcus Vinicius Alves Nunes (Avaliador Interno – PPGEE/UFPA)

Prof. Dr. Carlos Tavares da Costa Junior (Avaliador Interno – PPGEE/UFPA)

Prof. Dr. José Augusto Furtado Real (Avaliador Externo – UNAMA)

Prof. Dra. Maria Emília de Lima Tostes

(Coordenador do PPGEE/ITEC/UFPA)

#### **DEDICATION**

Dedico este trabajo primeramente a Dios y la Virgen María por haberme bendecido en este camino, darme una gran familia, brindarme salud y fuerza para poder seguir adelante.

Les dedico este trabajo también a mis padres, Jasmin Marcillo y Juan Carlos Lucas, por ser el pilar fundamental en mi vida, por ser mi ejemplo a seguir, por motivarme, por creer en mí en todo momento, y por haberme enseñado desde pequeño la importancia y valor del estudio.

Se lo dedico a mis hermanos, Jean y Tamara, por ser quienes me inspiran, sin saberlo, día a día a ser mejor persona, esperando que mis sacrificios les sirva de ejemplo para la superación, dándoles motivación para seguir adelante.

A todos mis familiares por brindarme una palabra de aliento siempre. A todos mis amigos que me han apoyado a lo largo de mi vida.

#### *ACKNOWLEDGMENT*

Agradezco a Dios por el don de la vida, por darme salud, motivación y por encontrar en él la fuerza para superar cualquier adversidad.

Agradezco a la Virgen de Schoenstatt por ser la Madres Tres Veces Admirable que resuelve todos mis problemas, gracias por haberme mostrado tu hermoso santuario donde encuentro paz.

Agradezco a mis padres por el apoyo incondicional que me ha hecho llegar hasta aquí (posgrado), muchas gracias por los valores inculcados, por brindarme todo lo necesario para afrontar la vida, gracias por ayudarme en todos los momentos en donde necesité de su ayuda, gracias por corregirme cuando era necesario y gracias por mostrarme ser los mejores padres que Dios me pudo dar.

Agradezco a mis hermanos por ser uno de los regalos más lindo de Dios.

Agradezco a mi familia en general, en especial a mis abuelos, tíos y primos, que con sus palabras de aliento han ayudado a crecer como persona. Gracias infinitas a mi Abuela Pancha y Abuelo Carlos, jamás podré devolverles todo el amor que me han brindado, lo que me llevo conmigo es la felicidad que siente por cada logro que consigo. De igual forma para mi Abuela Norma y Abuelo Claudio.

Agradezco a todos mis amigos que he conocido durante toda mi vida, gracias a ustedes que de una u otra forma han aportado su granito de arena para ser hoy la persona que soy. En especial a mis amigos, David Vaca, Jimmy González, Jonathan Moncada, Geovanny Arguello,

vi

Diego Villacreses, Julio Aguirre, Luis Ugarte, Hernán Ullón, Ronald Garcia, Ronald Orellana,

Leonardo Hernández, y demás, todos significan mucho para mí.

Agradeço aos meus amigos que conheci aquí, Markos, Erick, Renan, Leo, Luan, Rodrigo,

Ascir, Luis Otavio, Paulo, Sandy, Luise, Eder, Hugo, Cris, Mayara, Dudú. Obrigado a todos

vocês que transformaram minha vida no Brasil em uma estadia maravilhosa. Muito Obrigado

pelos bons momentos galera.

Agradeço aos colegas professores da UFPA, que me acolheram e me auxiliaram durante

meus estudos.

Agradeço ao meu orientador e Professor Walter Barra Junior, pelo ensino e orientação que

recebi durante todo o curso, colaborando significativamente para a realização deste trabalho. O

aprendizado foi grandioso para minha vida profissional e pessoal. Muito Obrigado.

Agradeço especialmente ao Professor Renan Landau de Medeiros, pela disponibilidade,

colaboração e ensinamentos que recebi durante o desenvolvimento da minha dissertação. Muito

Obrigado pela confiança.

Agradeço a UFPa e a CAPES pelo suporte acadêmico e financeiro prestado durante o

período de meu mestrado.

A todos, que foram importantes para mais essa conquista: meus amigos e familiares.

**MUITO OBRIGADO**

THANK YOU SO MUCH

**MUCHAS GRACIAS**

Epigraph

"Imagination is more important than knowledge. Knowledge is limited. Imagination encircles the world."

Albert Einstein

"There is nothing either good or bad, but thinking makes it so."

Hamlet Shakespeare

"Science is but a perversion of itself unless it has as its ultimate goal the betterment of humanity."

Nikola Tesla

# **CONTENS**

| Dedication                                                           | 1V  |

|----------------------------------------------------------------------|-----|

| Acknowledgment                                                       | V   |

| Epigraph                                                             | vii |

| List of Tables                                                       | X   |

| List of Figures                                                      | xi  |

| List of Abbreviations                                                | xiv |

| Resumo                                                               | XV  |

| Abstract                                                             | xvi |

| Chapter 1 - Introduction                                             | 1   |

| 1.1 State-of-the-Art                                                 | 1   |

| 1.2 Motivation and Justification                                     | 2   |

| 1.3 Definition of Objectives                                         | 5   |

| 1.3.1 General Purpose                                                | 5   |

| 1.3.2 Specific Objective                                             | 5   |

| 1.4 Outline                                                          | 5   |

| Chapter 2 - System Description                                       | 6   |

| 2.1 Introducction                                                    | 6   |

| 2.2 DC-DC Buck Converter                                             | 6   |

| 2.2.1 Conduction Modes of Buck Converter                             | 7   |

| 2.2.2 Dynamic of Buck Converter                                      | 12  |

| 2.3 Cascaded DC-DC Buck Converter System                             | 14  |

| 2.3.1 Buck Converter with Constant Power Load                        | 15  |

| 2.3.2 Instability in a DC-DC Buck Converter with Constant Power Load | 17  |

| 2.4 Stability Analysis of Multi-Converter Buck-Buck System           | 19  |

| 2.4.1 Stability of Multi-Converter Buck-Buck System                  | 19  |

| 2.4.2 Phase-Plane Analysis of Multi-Converter Buck-Buck System       | 21  |

| 2.4 Conclusion                                                       | 23  |

| Chapter 3 - Robust Parametric Control: Theory and Application        |     |

| in the design of robust controllers                                  | 24  |

| 3.1 Introduccion                                                     | 24  |

| 3.2 Brief Review of Robust Control Theory                            | 25  |

| 3.2.1 Robust Stability Analysis                                      | 25  |

| 3.2.2 Kharitonov Stability Theorem                                   | 26  |

| 3.3 SISO Robust Controller Design via Interval Pole-Placement        | 27  |

| 3.3.1 Linear Programing based on Kharitonov's Rectangle              | 30  |

| 3.3.2 Linear Programing based on Chebyshev Theorem                   | 31  |

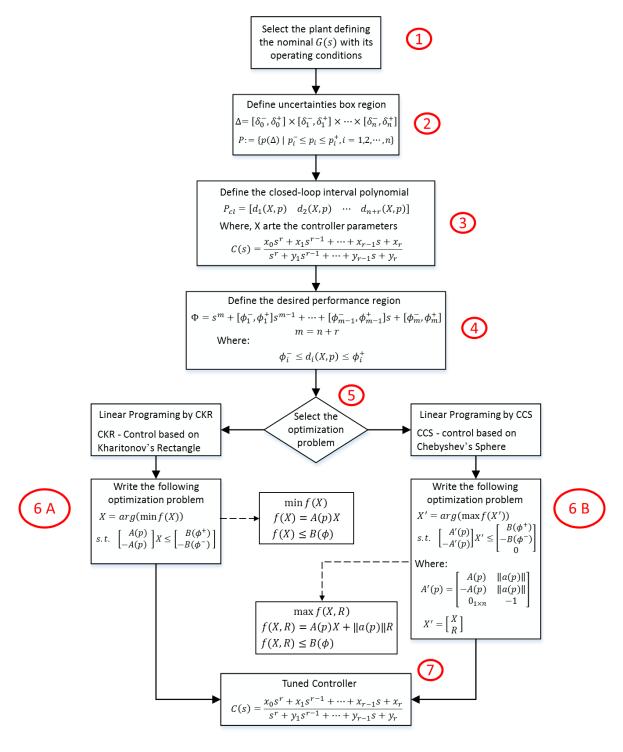

| 3.3.3 Summary of the Methodology                                                                       | 32   |

|--------------------------------------------------------------------------------------------------------|------|

| 3.4 conclusion of the chapter                                                                          | 34   |

| Chapter 4 - Description of Test Environments                                                           | 35   |

| 4.1 Introduccion                                                                                       | 35   |

| 4.2 Controller Design by Classical Pole-Placement                                                      | 35   |

| 4.3 Robust Controller Design by Interval Pole-Placement                                                | 36   |

| 4.4 Presentation and Description of the Simulation Environment of the Multi-Converter Buck-Buck System | 39   |

| 4.4.1 Simulation Environment of the Multi-Converter Buck-Buck System                                   | 40   |

| 4.4.2 Experimental Environment of the Multi-Converter Buck-Buck System                                 | 41   |

| 4.5 Description of Experiments                                                                         | 43   |

| 4.5.1 Evaluation of Voltage Mode Control of Source Converter.                                          | 44   |

| 4.5.2 Evaluation of Power Mode Control of Load Converter.                                              | 44   |

| 4.5.3 Performance Evaluation of Source Converter Feeding a CPL                                         | 44   |

| 4.6 Conclusion of the Chapter                                                                          | 45   |

| Chapter 5 - Results Analysis                                                                           | 46   |

| 5.1 Introduccion                                                                                       | 46   |

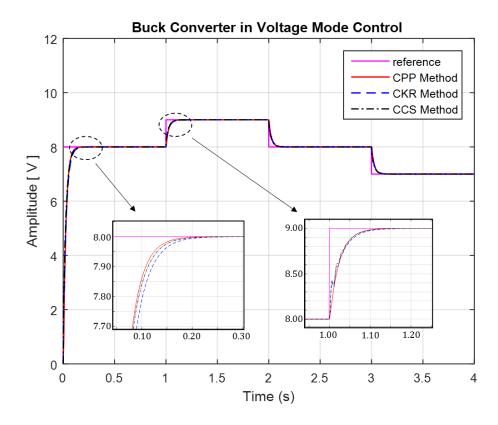

| 5.2 Evaluation of Voltage Mode Control of Source Converter                                             | 46   |

| 5.2.1 Simulation Environment                                                                           | 46   |

| 5.2.2 Experimental Environment                                                                         | 49   |

| 5.3 Evaluation of Power Mode Control of Load Converter                                                 | 52   |

| 5.3.1 Simulation Environment                                                                           | 52   |

| 5.3.2 Experimental Environment                                                                         | 53   |

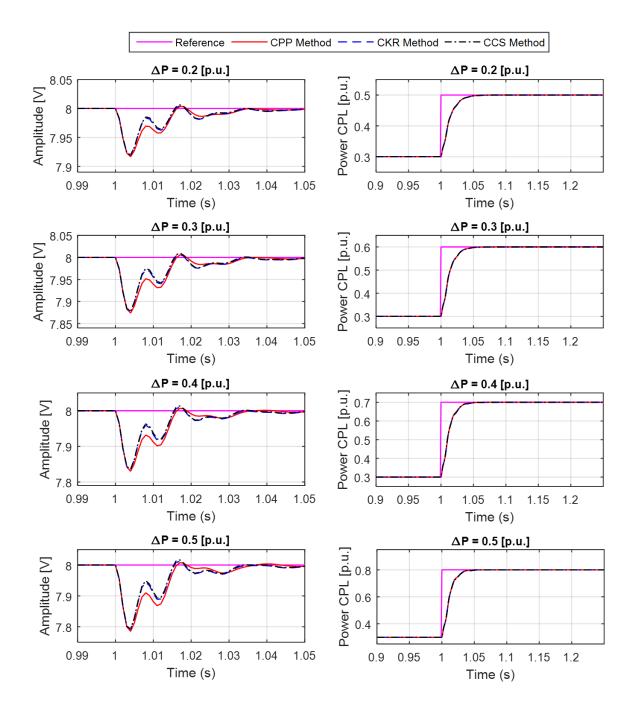

| 5.4 Performance Evaluation of Source Converter Feeding a CPL under Positive Power Variation            | 55   |

| 5.4.1 Simulation Environment                                                                           | 55   |

| 5.4.2 Experimental Environment                                                                         | 60   |

| 5.5 Performance Evaluation of Source Converter Feeding a CPL under Negative Power Variation            | n 65 |

| 5.5.1 Simulation Environment                                                                           | 65   |

| 5.5.2 Experimental Environment                                                                         | 70   |

| 5.6 Conclusion of the Chapter                                                                          | 75   |

| <b>Chapter 6 - Final Considerations of the Dissertation and Recommendations for Future Works</b>       | s 76 |

| 6.1 Final Considerations                                                                               | 76   |

| 6.2 Recommendations for Future Works                                                                   | 77   |

| References                                                                                             | 78   |

# LIST OF TABLES

| Table 2.1. Values for the physical parameters of the multi-converter buck-buck system.                                                                     | 20 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2. Eigenvalues of the linearized multi-converter buck-buck system.                                                                                 | 21 |

| Table 4.1. Performance specifications for the controller design of source converter.                                                                       | 35 |

| Table 4.2. Performance specifications for the controller design of load converter.                                                                         | 36 |

| <b>Table 4.3.</b> Values for the physical parameters of the multi-converter buck-buck system with its parametric uncertainties for the experimental tests. | 37 |

| Table 4.4. Parameters value for the designed controllers.                                                                                                  | 38 |

| Table 4.5. Discrete parameters value for the designed controllers.                                                                                         | 39 |

# LIST OF FIGURES

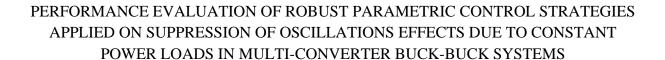

| Figure 2.1. Buck converter topology.                                                                                                                                                                                             | 1          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

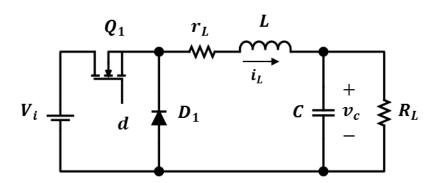

| Figure 2.2. Buck Power Stage States.                                                                                                                                                                                             | 8          |

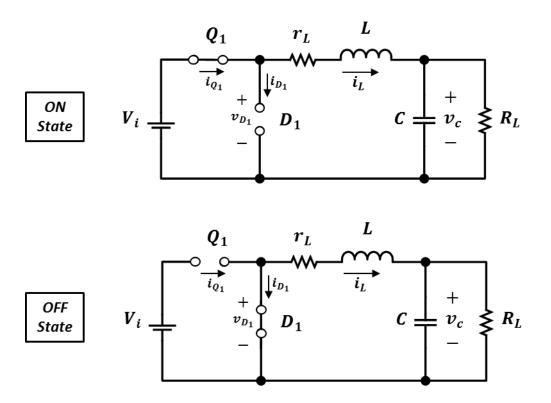

| Figure 2.3. Typical waveforms for Buck Power Stage States.                                                                                                                                                                       | 9          |

| Figure 2.4. Boundary between Continuous and Discontinuous Mode.                                                                                                                                                                  | 9          |

| Figure 2.5. Discontinuous Current Mode.                                                                                                                                                                                          | 10         |

| Figure 2.6. Discontinuous-Mode Buck Power Stage Waveforms.                                                                                                                                                                       | 11         |

| <b>Figure 2.7.</b> Buck Converter system in series connection: (A) Cascaded system with N-converter. (Figure 2.7.) Voltage mode control for the k-th converter.                                                                  | B)<br>14   |

| <b>Figure 2.8.</b> Cascaded buck converter with two power stages. (A) Diagram of the cascaded converter (B) Source converter loaded by a CPL. (C) Voltage mode control for source converter. (D) Tight regulated load converter. | ers.<br>15 |

| Figure 2.9. Input "V –I" characteristics of the CPL.                                                                                                                                                                             | 16         |

| Figure 2.10. The negative incremental impedance behavior of CPL.                                                                                                                                                                 | 17         |

| Fig. 2.11. Phase-portrait of source converter loaded with a CPL ( $Vi = 15 \text{ V}$ , $D1 = 0.424$ ,                                                                                                                           | 22         |

| CPL Power $Po = 0.5 \text{ p. u.}, L = 2 \text{ mH}, C = 2000 \mu\text{F}).$                                                                                                                                                     | 22         |

| Fig. 2.12. Phase-portrait of load converter (Input DC voltage $= 6 \text{ V}$ , $D2 = 0.6$ ,                                                                                                                                     | 22         |

| $Po = 0.5 \text{ p. u.}, L = 2 \text{ mH}, C = 2000 \mu\text{F}).$                                                                                                                                                               | 22         |

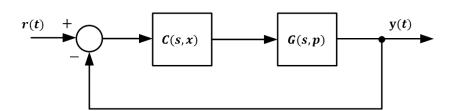

| Figure 3.1. Closed-loop system block-diagram.                                                                                                                                                                                    | 27         |

| Figure 3.2. Largest ball B inscribed in P.                                                                                                                                                                                       | 31         |

| Figure 3.3. Flowchart of methodology for designing of robust controllers.                                                                                                                                                        | 33         |

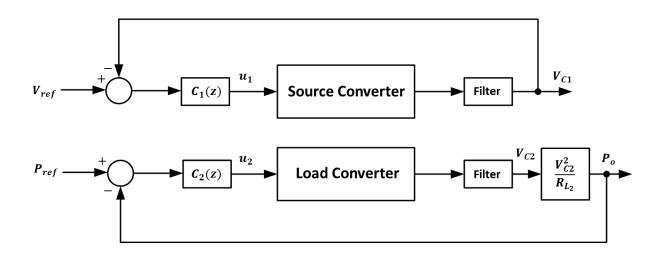

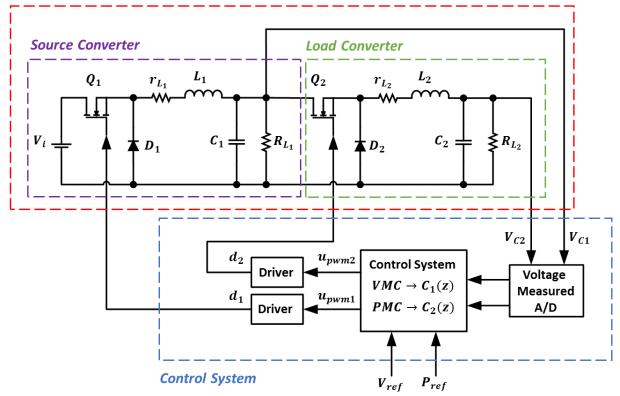

| Figure 4.1. Control-generalized block-diagram applying to multi-converter buck-buck system                                                                                                                                       | 39         |

| Figure 4.2. The electric circuit of the multi-converter buck-buck system.                                                                                                                                                        | 40         |

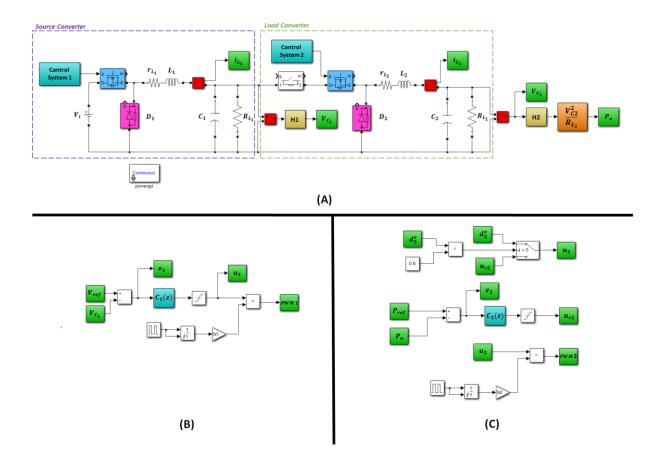

| <b>Figure 4.3.</b> (A) Electric circuit of the multi-converter buck-buck system by Matlab/Simulink. (B) Control subsystem 1. (C) Control subsystem 2.                                                                            | 41         |

| Figure 4.4. (A) Generic diagram of the subsystems developed. (B) Block diagram of the developed                                                                                                                                  |            |

| hardware system and actuation of the system control signal.                                                                                                                                                                      | 42         |

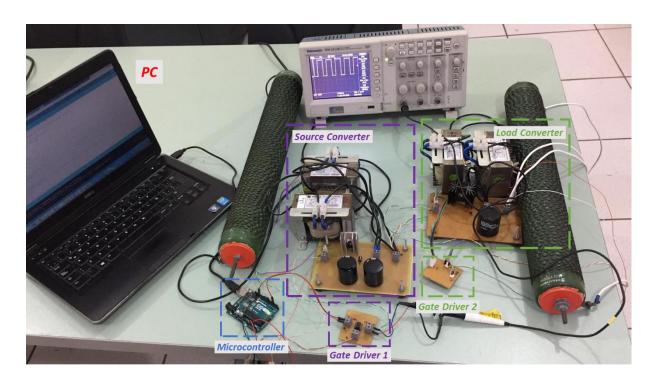

| <b>Figure 4.5.</b> Multi-converter buck-buck system.                                                                                                                                                                             | 43         |

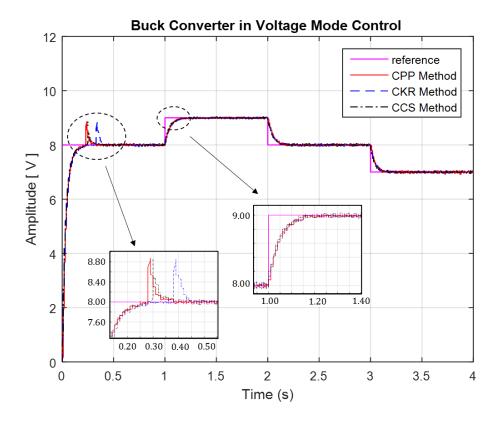

| <b>Figure 5.1.</b> Source Converter operating in closed-loop with a PID controller structure.                                                                                                                                    | 47         |

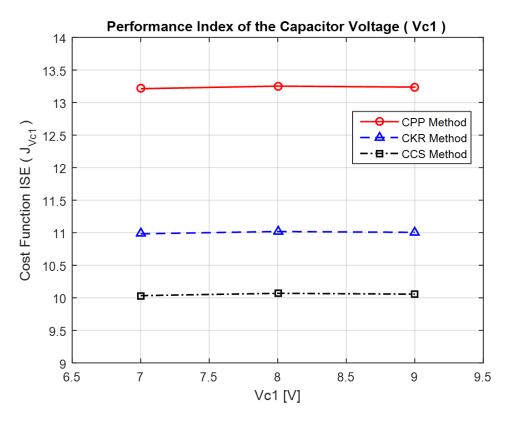

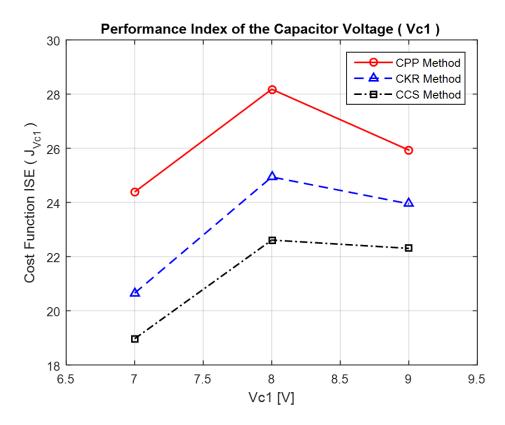

| <b>Figure 5.2.</b> The cost function ISE of the simulated system when the source converter is subjected to reference voltage variation using a PID control structure.                                                            | 48         |

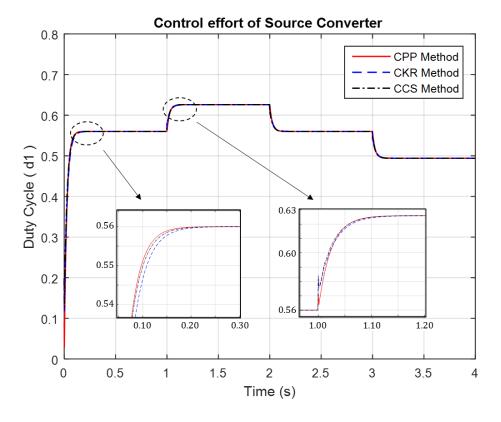

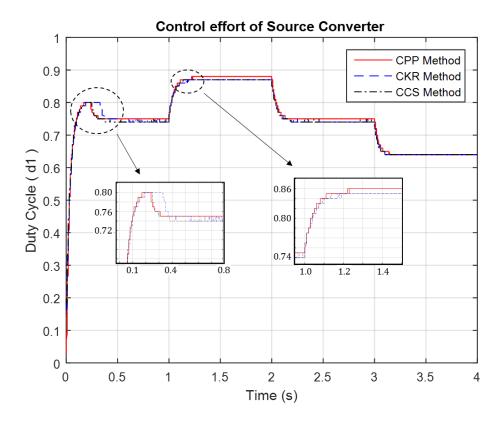

| <b>Figure 5.3.</b> The control effort test, when the source converter is subjected to a reference voltage variation using a PID control structure.                                                                               | 48         |

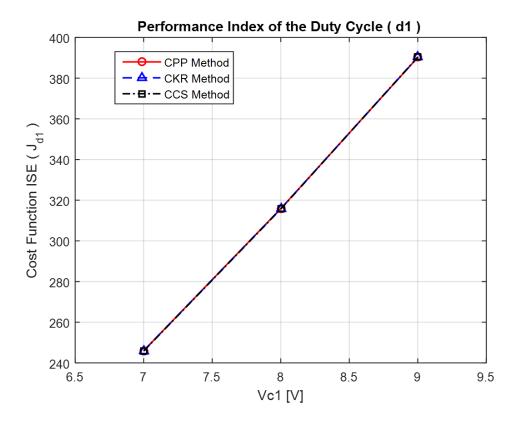

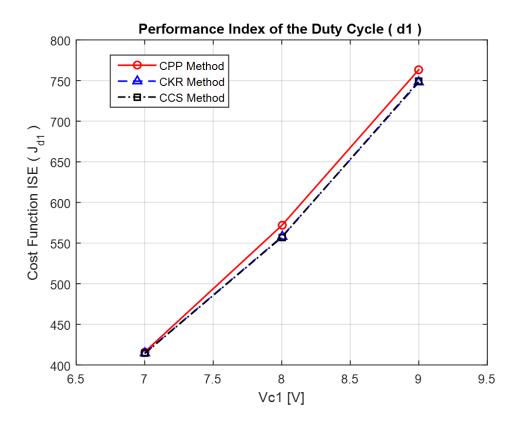

| <b>Figure 5.4.</b> The cost function ISE of control effort of the simulated system when the source convert is subjected to a reference voltage variation using a PID control structure.                                          | er<br>49   |

| <b>Figure 5.5.</b> Experimental test of the source converter using a PID control structure when the system subjected to a reference voltage variation.                                                                           | is<br>50   |

67

| <b>Figure 5.6.</b> The cost function ISE of the experimental data collected system when the source converter is subjected to a reference voltage variation using a PID control structure.                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 5.7.</b> The experimental control effort test, when the source converter is subjected to a reference voltage variation using a PID control structure.                                                                  |

| <b>Figure 5.8.</b> The cost function ISE of control effort of the experimental data collected when the source converter is subjected to a reference voltage variation using a PID control structure.                             |

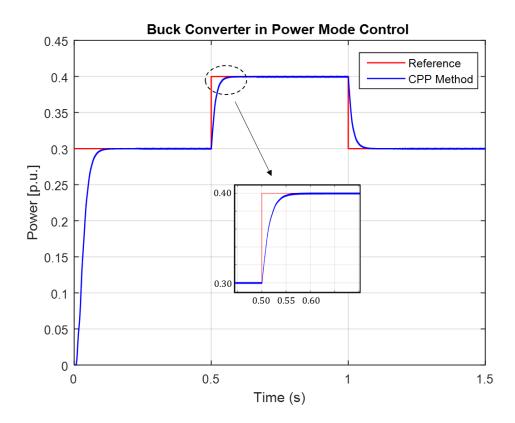

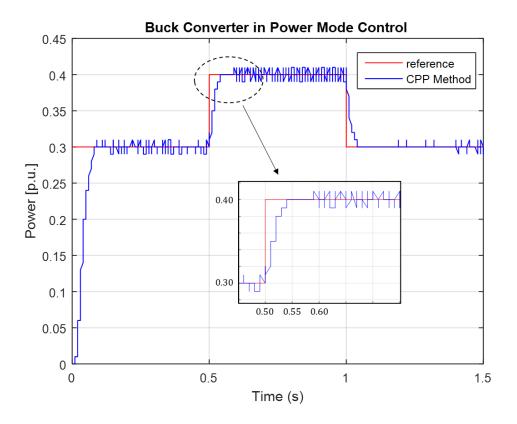

| <b>Figure 5.9.</b> Simulated test of the load converter using a PID control structure when the system is subjected to a reference power variation.                                                                               |

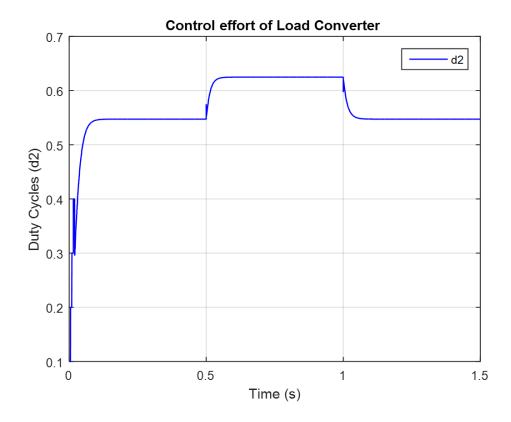

| <b>Figure 5.10.</b> The simulated control effort test, when the load converter is subjected to a reference power variation using a PID control structure.                                                                        |

| <b>Figure 5.11.</b> Experimental test of the load converter using a PID control structure when the system is subjected to a reference power variation.                                                                           |

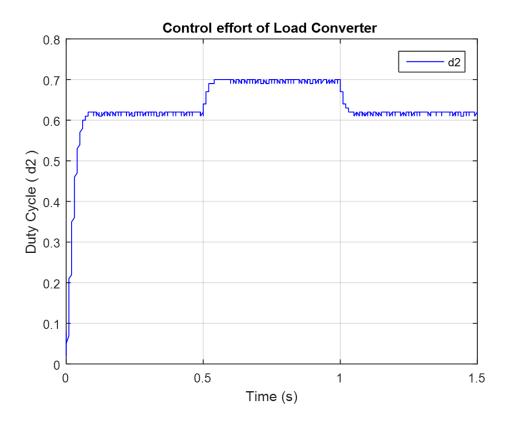

| <b>Figure 5.12.</b> The experimental control effort test, when the load converter is subjected to a reference power variation using a PID control structure.                                                                     |

| <b>Figure 5.13.</b> Simulated test of the multi-converter buck-buck system when the source converter is feeding a CPL using a PID control structures when the system is subjected to a positive variation of power reference.    |

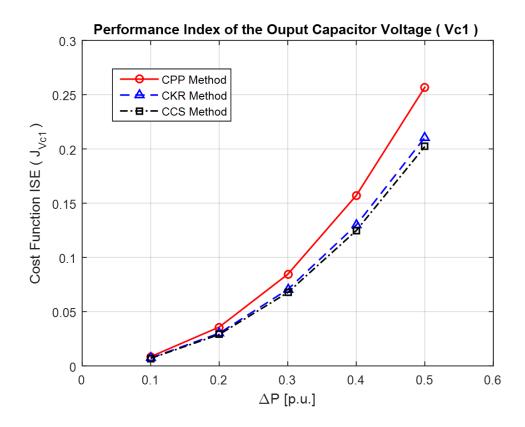

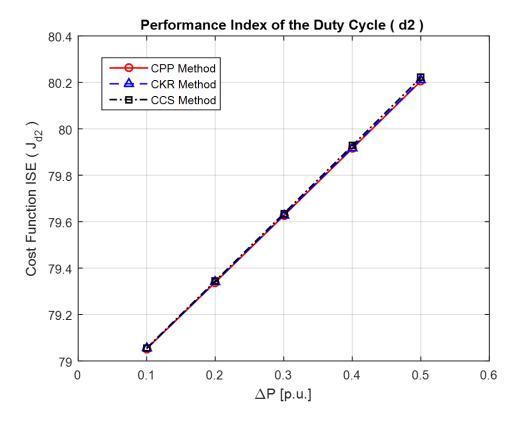

| <b>Figure 5.14.</b> The simulated cost function ISE of source converter when multi-converter buck-buck system is subjected to a positive variation of power reference using a PID control structure.                             |

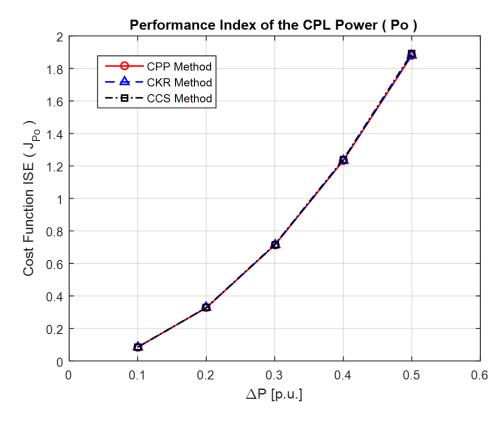

| <b>Figure 5.15.</b> The simulated cost function ISE of load converter when multi-converter buck-buck system is subjected to a positive variation of power reference using a PID control structure.                               |

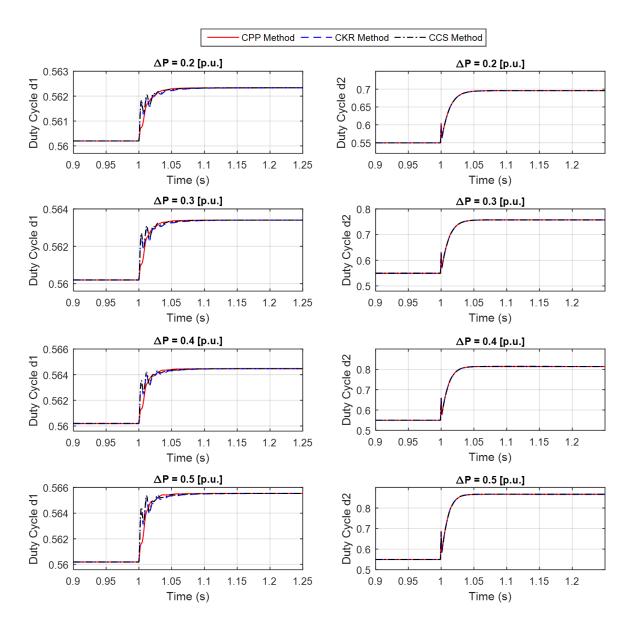

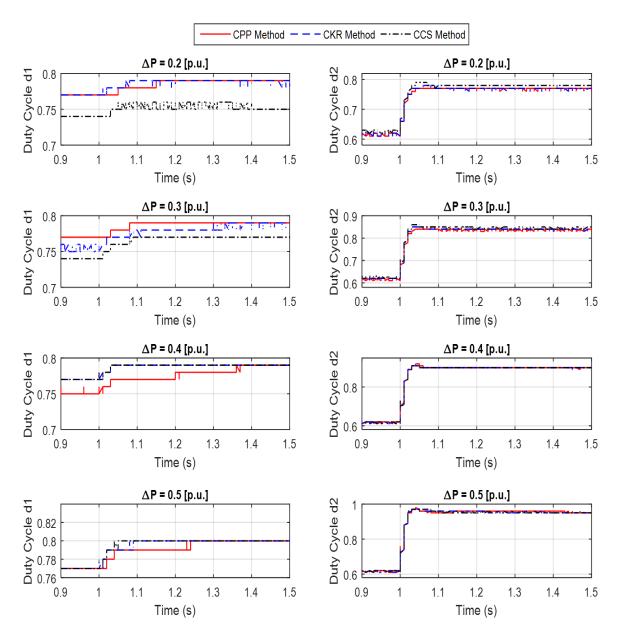

| <b>Figure 5.16.</b> The control effort test of multi-converter buck-buck system, when the simulated system is subjected to a positive variation of power reference using a PID control structures.                               |

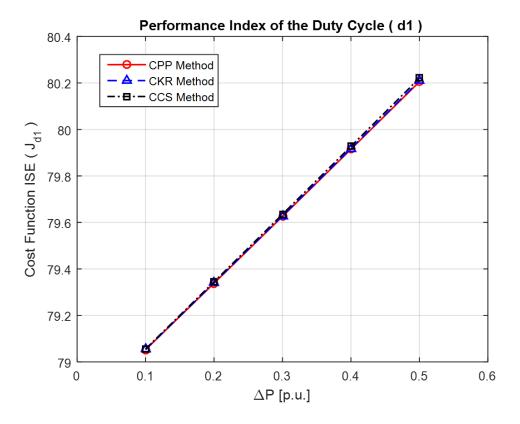

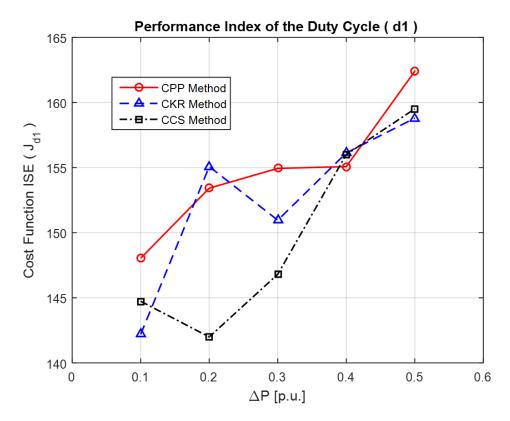

| <b>Figure 5.17.</b> The cost function ISE of control effort of source converter when the simulated system is subjected to a positive variation of power reference using a PID control structure.                                 |

| <b>Figure 5.18.</b> The cost function ISE of control effort of load converter when the simulated system is subjected to a positive variation of power reference using a PID control structure.                                   |

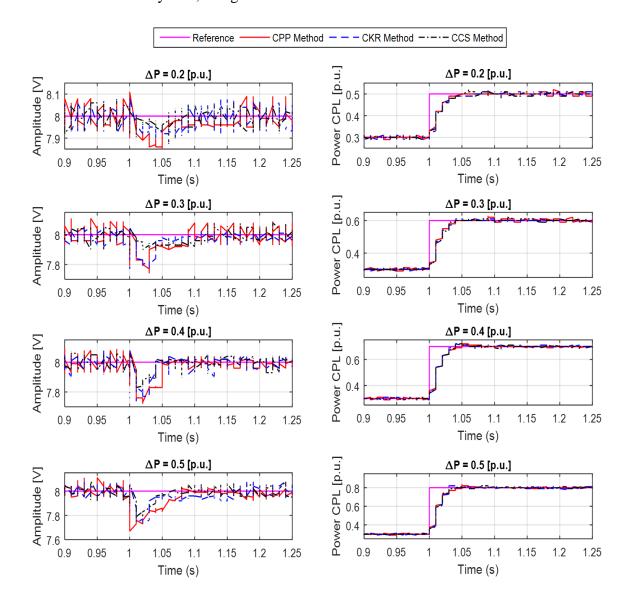

| <b>Figure 5.19.</b> Experimental test of the multi-converter buck-buck system when the source converter is feeding a CPL using a PID control structures when the system is subjected to a positive variation of power reference. |

| <b>Figure 5.20.</b> The experimental cost function ISE of source converter when multi-converter buck-buck system is subjected to a positive variation of power reference using a PID control structure.                          |

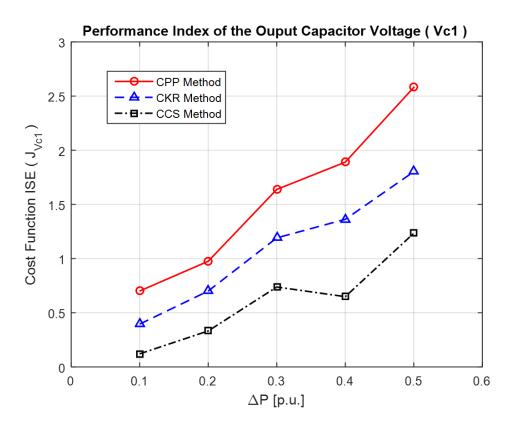

| <b>Figure 5.21.</b> The experimental cost function ISE of load converter when multi-converter buck-buck system is subjected to a positive variation of power reference using a PID control structure.                            |

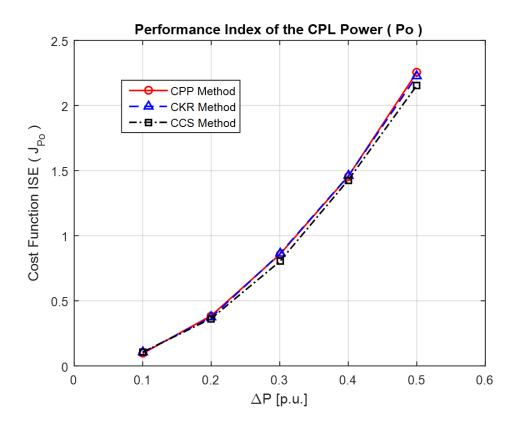

| <b>Figure 5.22.</b> The control effort test of multi-converter buck-buck system, when the system is subjected to a positive variation of power reference using a PID control structures.                                         |

| <b>Figure 5.23.</b> The cost function ISE of control effort of source converter when the experimental system is subjected to a positive variation of power reference using a PID control structure.                              |

| <b>Figure 5.24.</b> The cost function ISE of control effort of load converter when the experimental system is subjected to a positive variation of power reference using a PID control structure.                                |

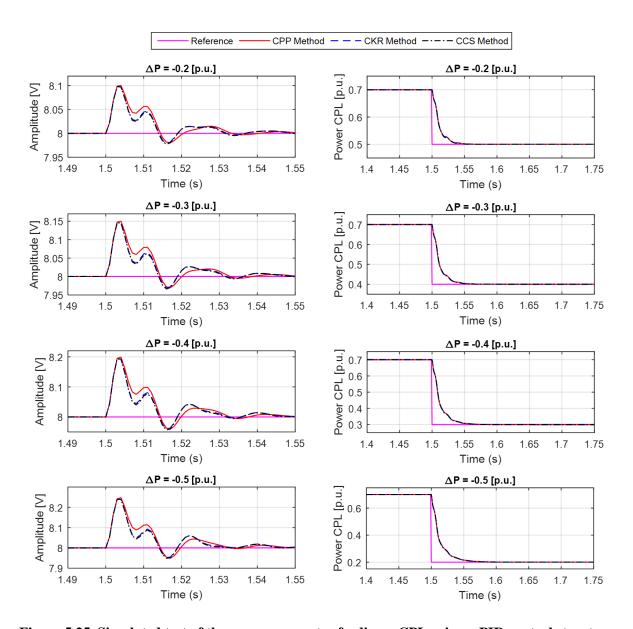

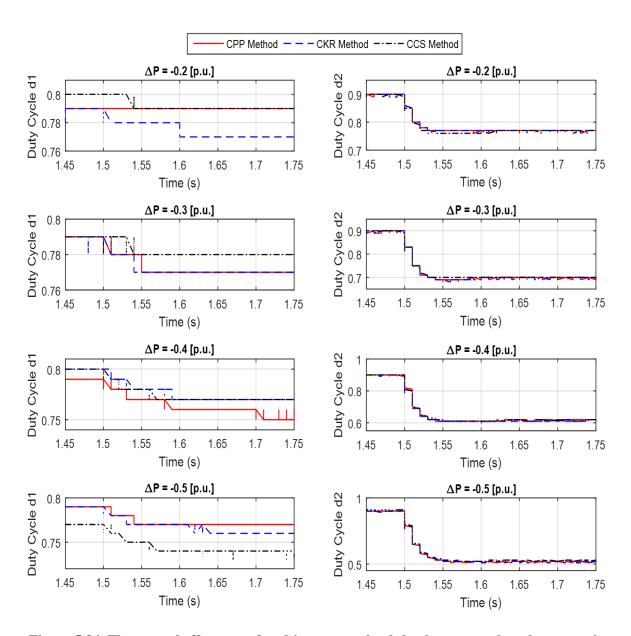

| <b>Figure 5.25.</b> Simulated test of the source converter feeding a CPL using a PID control structure when the simulated system is subjected to a negative variation of power reference.                                        |

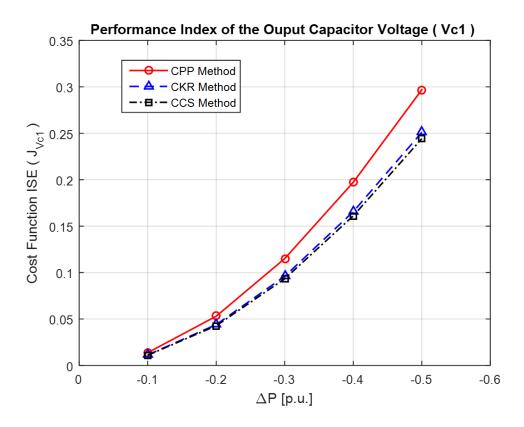

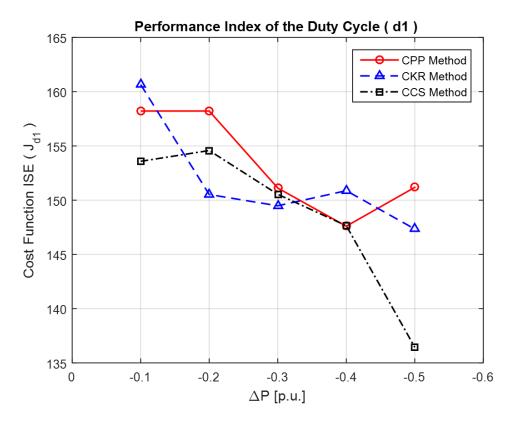

| <b>Figure 5.26.</b> The simulated cost function ISE of source converter when multi-converter buck-buck system is subjected to a negative variation of power reference using PID control structure.                               |

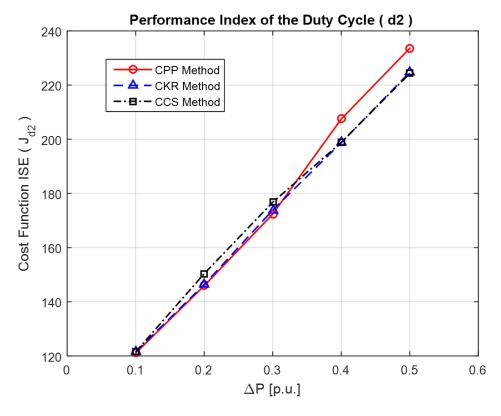

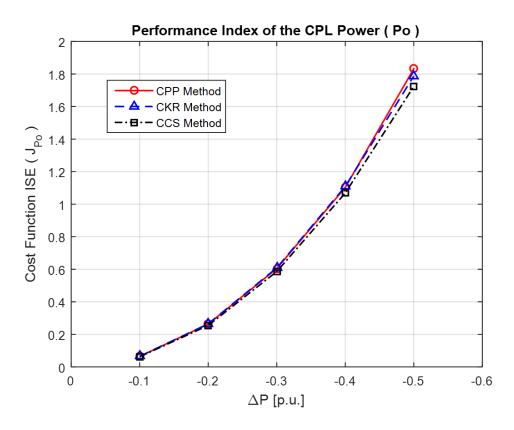

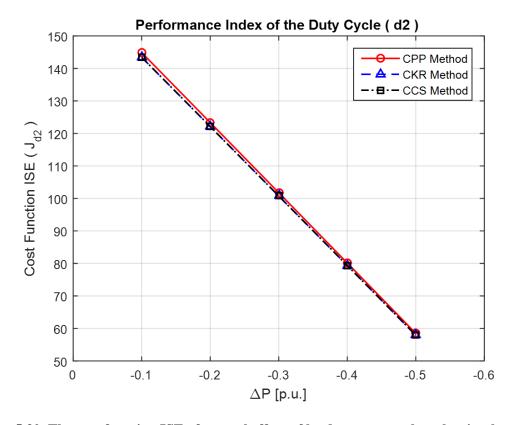

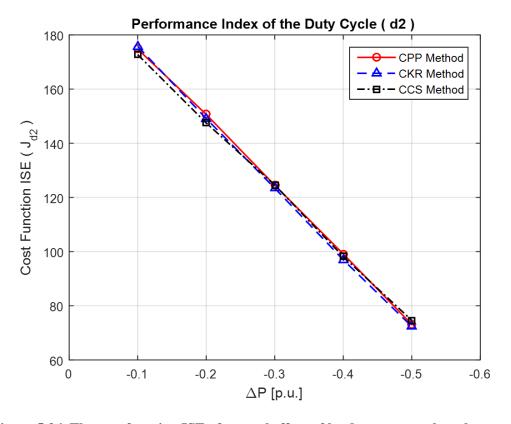

| <b>Figure 5.27.</b> The simulated cost function ISE of control effort of load converter when simulated system is subjected to a negative variation of power reference using a PID control structure. | 7 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

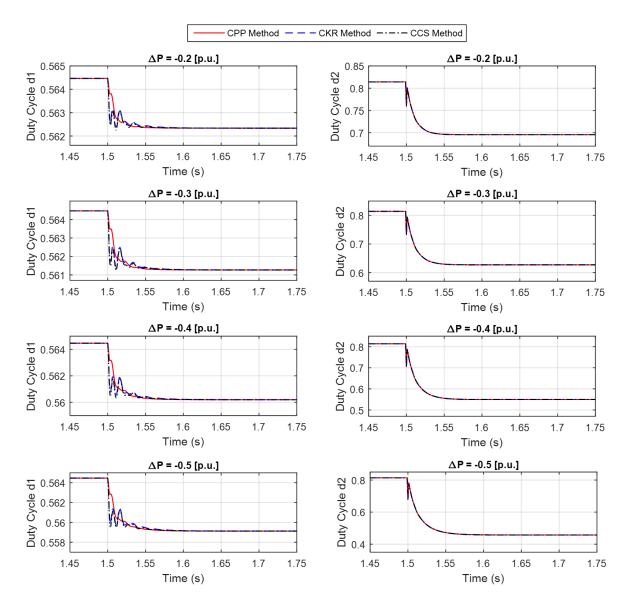

| <b>Figure 5.28.</b> The control effort test of multi-converter buck-buck system, when the simulated system is subjected to a negative variation of power reference using a PID control structures.   | 3 |

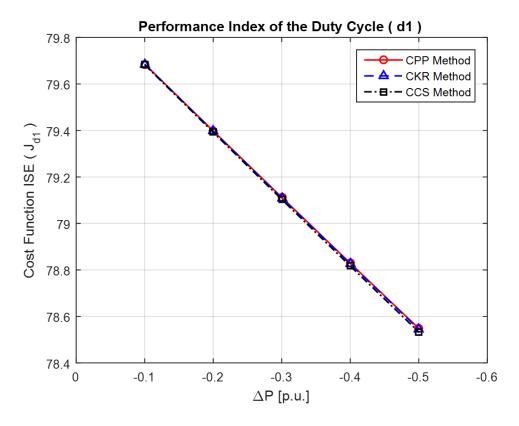

| <b>Figure 5.29.</b> The cost function ISE of control effort of source converter when the simulated system is subjected to a negative variation of power reference using a PID control structure.     | ) |

| <b>Figure 5.30.</b> The cost function ISE of control effort of load converter when the simulated system is subjected to a negative variation of power reference using a PID control structure.       | ) |

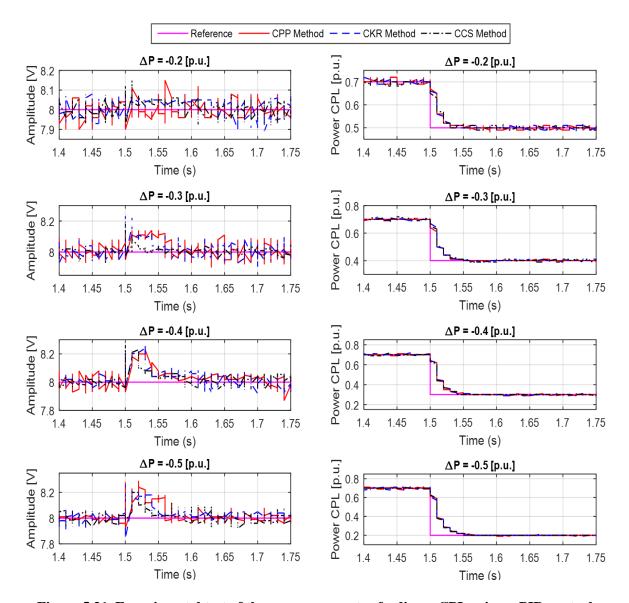

| <b>Figure 5.31.</b> Experimental test of the source converter feeding a CPL using a PID control structure when the system is subjected to a negative reference power variation.                      | ) |

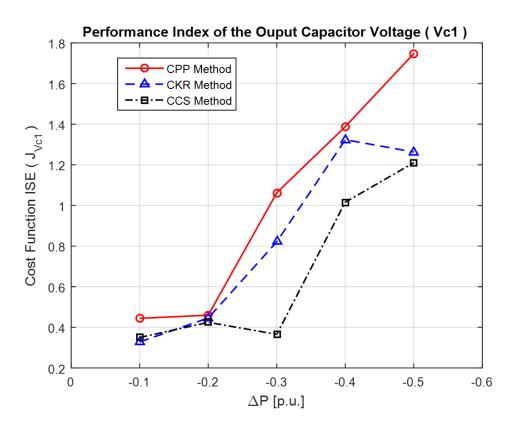

| <b>Figure 5.32.</b> The cost function ISE of source converter when the multi-converter buck-buck system is subjected to a negative reference power variation using a PID control structure.          |   |

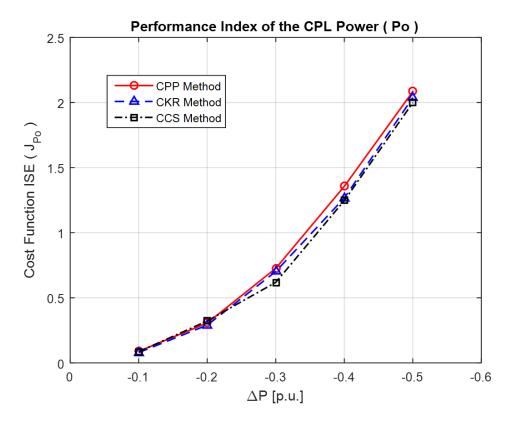

| <b>Figure 5.33.</b> The cost function ISE of load converter when the multi-converter buck-buck system is subjected to a negative reference power variation using a PID control structure.            | 2 |

| <b>Figure 5.34.</b> The control effort test of multi-converter buck-buck system, when the system is subjected to a positive reference power variation using a PID control structures.                | 3 |

| <b>Figure 5.35.</b> The cost function ISE of control effort of source converter when the system is subjected to a negative reference power variation using a PID control structure.                  | 1 |

| <b>Figure 5.36.</b> The cost function ISE of control effort of load converter when the system is subjected to a negative reference power variation using a PID control structure.                    | 1 |

# LIST OF ABBREVIATIONS

PWM Pulse Width-Modulation

CPL Constant Power Load

SMC Sliding mode control

DC Direct Current

RPC Robust Parametric Control

LP Linear Programming

PID controller Proportional-Integral-Derivative controller

ISE Integral Square Error

DCM Discontinuous Conduction Mode

CCM Continuous Conduction Mode

CPP Classical Pole-Placement

VMC Voltage Mode Control

PMC Power mode control

CKR Control based on Kharitonov's Rectangle

CCS Control based on Chebyshev's Sphere

ZOH Zero-order hold

SISO system Single-Input Single-Output system

LMI Linear Matrix Inequality

## **RESUMO**

Conversores chaveados são sistemas amplamente utilizadas em aplicações industriais. Tais sistemas operam via controle em malha fechada e, dessa forma, os aspectos de estabilidade e desempenho em malha fechada devem ser assegurados pelo projetista. Recentemente, o emprego de sistemas com múltiplos conversores vem se tornando comum em uma ampla gama de aplicações. A interação entre os sistemas de controle os múltiplos conversores pode levar o sistema a operar com reduzidas margens de estabilidade ou com um baixo desempenho dinâmico. Portanto, a estabilidade de um sistema com conversores operando em cascata é uma grande preocupação para aplicações reais. A instabilidade em sistemas em cascata pode ocorrer devido à carga de potência constante (CPL), que é um comportamento dos conversores quando se encontram regulados. As CPLs exibem comportamento de resistência negativa incremental, causando um alto risco de instabilidade em conversores interligados. Dessa forma, a mitigação desse problema é uma questão importante no projeto da fonte de alimentação comutada de múltiplos estágios, de modo a garantir a estabilidade de todo o sistema. No entanto, algumas dificuldades estão presentes além da CPL, por exemplo, não linearidades fortes, devido à presença do elemento indutivo, além das incertezas em relação aos valores nominais dos componentes discretos que compõem o sistema. Neste trabalho é realizado um estudo experimental do desempenho das metodologias de controle robusto paramétrico aplicadas ao problema de mitigar o efeito adverso de cargas do tipo CPL, em um sistema com dois conversores buck operando em cascata (sistema buck-buck). Vários testes foram desenvolvidos utilizando tanto uma planta experimental quanto via simulação computacional em Matlab/ Simulink, quando o sistema multiconversor buck-buck é submetido a uma variação de potência. Os resultados mostram o melhor desempenho das metodologias propostas.

Palavra-chave: sistema multiconversor; controle robusto paramétrico; CPL; variação paramétrica; teorema de estabilidade de kharitonov; Teorema de Chebyshev.

## **ABSTRACT**

Multi-converter electronic systems are becoming widely used in many industrial applications; therefore, the stability of the cascaded system is a big concern to real-world power supplies applications. Instability in cascaded systems may occur due to the constant power load (CPL), which is a behavior of the tightly regulated converters. CPLs exhibit incremental negative resistance behavior causing a high risk of instability in interconnected converters; therefore, the mitigation of this problem is an important issue in the multiple-stage switched mode power supply design. Thus, it is important to guarantee stability of the whole system. However, some difficulties remains besides the CPL, e.g., non-linearities due to the inductive element and uncertainties due to imprecision of mathematical models and/or variation of nominal values of the discrete elements that compose the DC/DC buck converter. Aiming to evaluate the performance of the proposed robust methodologies in this work to mitigate the instability problem caused by a CPL, several tests were developed by using an experimental plant and Matlab/Simulink, when the multi-converter buck-buck system is subjected a variation of power reference. The results show the improved performance of the proposed methodologies.

Key-word: multi-converter system; robust control; robust parametric control; constant power load; parametric variation; buck converter; kharitonov stability theorem; chebyshev theorem.

#### CHAPTER 1

## INTRODUCTION

#### 1.1 STATE-OF-THE-ART

Nowadays, DC-DC converters are increasingly used in industrial applications due to their simplicity in structure, high power efficiency, low cost and high reliability [1], [2]. Some modern industries, whose processes demand high dynamic performance, have applied different types of converters for applications such as in variable speed DC motor drivers [3], renewable energy systems [4]-[6], transportation systems [7], [8], hybrid energy storage system [9], [10], communications systems [11]. In several of these applications, converters are controlled by switching through Pulse Width-Modulation (PWM) to transfer power from a power source to loads having a constant power characteristic. Because of switching, the converter converters have some inherent nonlinear behaviors [12], [13]. Therefore, it is a challenging task to ensure the stability, transient performance and higher efficiency of such converters [13]. The nonlinear behavior, due to switching operation, has been usually neglected while designing the converter [2]. One important converter topology is the DC-DC buck converters where the required output voltage is lower than the source voltage. DC-DC buck converters are typically dynamical nonlinear systems and their control problems are well acknowledged as a challenging issue [14]-[16]. The main reasons are: load variations, power source variations, inevitable parameter uncertainties and exogenous disturbances. All these uncertainties could lead to instability and performance degradation.

On the other hand, cascaded converters have a basic configuration that consists of two converters in series connection, where the first is a source converter while the second one is a load converter. The source converter maintains a regulated dc voltage on the intermediate bus, and the load converter convert the intermediate bus voltage to tightly regulated outputs for the

next system stage or load. When a converter tightly regulates its output, it behaves as a Constant Power Load (CPL), so load converter acts as a CPL when tightly regulated [18] and its dynamic response is faster than the dynamic response of the source converter. If the source converter is faster than the load converter, then it will compensate for disturbances and will regulate its output before the feedback loop of the load converter reacts to disturbances. Therefore, the load converter will not act as a perfect CPL for the feeding converter [19]-[25]. Different from a resistive load, CPL is a nonlinear load with variable negative impedance characteristics, i.e. the input current increases/decreases with a decrease/increase in its terminal voltage [19]-[25]. Because of the negative impedance characteristics of CPL, the system may become unstable, which may lead the system into oscillation or failure, and stress or damage the system equipment when feeding a CPL [21]-[25]. For this issue, CPLs are receiving more attention of researchers to give solutions aiming at to cancel or compensate the instability caused by CPL.

#### 1.2 MOTIVATION AND JUSTIFICATION

Traditionally, the stability analysis and controller design of cascaded dc-dc converters is carried out by using the impedance criterion applied to averaged and linearized models [23]-[26]. The load converter under a tight control is conventionally modeled constant power load (CPL) for stability analysis or for controller design [23]-[26].

In order to mitigate the destabilizing effect of CPL, several methods have been proposed, such as passive and active damping [27]-[29], Lyapunov redesign control [8], nonlinear feedback linearization [30]-[33], sliding mode control (SMC) [34], [35], fuzzy control [36], and robust control [37], [38]. In addition, the robust parametric control methodology can be found in the literature to control dc-dc power converters [39]-[41].

The controller design is usually based on the linear approximation of nonlinear dynamics of the converter. Linear controllers are usually used to regulate the output voltage

[14], [42] of converters. However, conventional controllers may experience a sensible performance deterioration under varying operating conditions [39]-[41]. In order to assure robustness against parameter uncertainties, linear controllers must be designed by using robust control theory. Therefore, the controller can be designed to cope with a pre-specified range of parameter uncertainties, load variations, or a wide variation of operating points. Besides of that, the performance of the DC-DC converters is also affected by external disturbance, which may cause instability that usually appear due to the measurement noises [40]-[41]. Therefore, the controller design process must ensure the performance robustness.

In research on dynamic systems with parametric uncertainties, the techniques that deal with this problem have been studied extensively over the last 40 years [42], [43]. In this context, control strategies, which aim to implement adaptive, predictive and fuzzy control algorithms, have been widely studied for the resolution of control problems of systems with parametric uncertainties. However, these strategies, being able to offer efficient and satisfactory results, can make the implementation and operation of the process more complex [44].

Within the context of solutions for process control, one of the areas that have received great research efforts from the scientific community is Robust Parametric Control (RPC) Theory. Such classes of robust control approaches take into account the available apriori information about possible range of plant's parameters, around their respective nominal values [45]. The RPC gained greater attention from academia since the 1980s because of Kharitonov's work, who developed the so-called seminal Kharitonov stability Theorem. Among the several methods of solution to the problem of controlling plants with parametric uncertainties, in the present work, are highlighted the use of Linear Programming (LP) approach [46] and the Chebyshev Theorem [47]. These methods, when combined, serve to design optimal and robust controllers.

In this work, a design trend is presented for Proportional-Integral-Derivative (PID) controllers' family based on parametric robust control theory. The controller designed is applied to a source converter in a multi-converter system to suppress of oscillations effects due to constant power loads in multi-converter buck-buck systems, aiming to reduce the control effort when the system is operating outside its nominal operating point. The motivation arises from the difficulty of relating parametric robust control theory to conventional design methods. In conventional methods, the goal is to design a controller with fixed parameters from a plant with fixed parameters too. However, robust parametric control presents a different form of controller development, in which the modelling of the systems is developed with the plant parameters represented by real intervals (not fix). From the method presented in [46], it is possible to develop controllers designed for an interval domain and still with fix parameters. The reason for choosing the controllers of the PID family is justified by the fact that it is the most popular controller in the industrial environment [48]. In [46] and [49], a linear programming approach is used to provide necessary conditions on the fixed-order controller design for robust stability of the closed-loop systems. In [40], the design of a robust controller via linear programming is presented in comparison to a conventional design technique applied to the output voltage control of a DC-DC buck converter. In these works, only linear programming approach is used to solve the optimization problem proposed for tuning of the controllers parameters.

Theoretical contributions of the RPC combined with conventional control techniques emphasize the importance of the RPC in different current applications such as drones [50], industrial processes [51], [39] and power systems [52]. Therefore, in this work a control strategy is proposed combining the linear programing approach [46] with Chebyshev Theorem [47], to optimize the parameters of an interval robust controller, providing better control performance. In addition, robust controller design is presented with robust stability guaranteed according to Kharitonov Theorem.

#### 1.3 DEFINITION OF OBJECTIVES

#### 1.3.1 General Purpose

To evaluate robust control strategies applied to a multi-converter buck-buck system in order to stabilize the oscillations of whole system caused by a constant power load.

## 1.3.2 Specific Objective

- To analyze the dc-dc buck converter dynamics by feeding a constant power load.

- To carry out an experimental and simulation evaluation of robust control strategies

applied to the multi-converter buck-buck system, when it is subjected to a variation of

power reference.

- To carry out the evaluation of the Integral Square Error (ISE) cost function, in order to verify the robustness and performance of the control strategies evaluated, when the multi-converter buck-buck system is subjected to a variation of power reference.

#### 1.4 OUTLINE

The remainder of this work is organized as follows: Chapter 2 presents a brief review about the multi-converter buck-buck system; Chapter 3 presents a brief review about parametric robust control background in addition to the design methodologies for robust controllers. Chapter 4 presents the methodologies developed in this study, describing the simulation environment, as well as the experimental environment, and then the experiments to be performed in this work are described. Chapter 5 presents an assessment of the simulation results and experimental data. Finally, Chapter 6 presents the final considerations of the dissertation and recommendations for future works.

#### CHAPTER 2

## SYSTEM DESCRIPTION

#### 2.1 INTRODUCCTION

In a DC network, the operation of DC-DC power converters is similar to transformers in AC networks, that is, increase or decrease the input voltage, generating an output power equal, in ideal conditions, without the use of external power. These converters present six main topologies: *Buck, Boost, Buck-Boost, Cuk, Sepic e Zeta*; or some derivations of them [12]. In addition, they can be unidirectional, with only a conduction sense, or bidirectional, whose conduction sense can be reversed. According to architecture of the filters, it may be classified them according to their order [54].

Multi-converter cascading power systems are very common in most application in industry [3]-[11]. When a power converter tightly regulates its output, it behaves as a CPL [18]. CPLs have a negative incremental resistance, which tends to destabilize the power system [23]-[25].

In this chapter, the study system is presented. First for a buck converter, the topology, operation and conduction modes and dynamic are analyzed. Then the cascaded converter system is presented, analyzing its dynamics and instability issue due to CPL.

#### 2.2 DC-DC BUCK CONVERTER

DC-DC converters are electronic devices that convert a direct voltage or a direct current value to a different level. This conversion can be obtained with the combination of an inductor and/or a capacitor, and a solid-state device operating in the high frequency switching mode. In the buck converter case, also called Step-Down or voltage drop, the output has a lower voltage

than the input voltage. A typical topology of buck converter shown in Fig. 2.1. d is switch, L is inductance, C is capacitance,  $D_1$  is freewheel diode,  $R_L$  is load resistance.  $i_L$  is the current of inductance L,  $V_i$  is input voltage,  $v_c$  is output capacitor voltage.

Buck converter operation can be analyzed in two alternate states for each period of the digital control signal [53],[54]. First state occurs when MOSFET,  $Q_1$ , is "on" and diode,  $D_1$ , is "off", causing the energy transfer from the source to the inductor, capacitor and load, charging the inductor and capacitor, as well as feeding the load. In second stage,  $Q_1$  is "off", and  $D_1$  is "on", so that the inductor current behaves as the power source for the load, causing its gradual discharge. When inductor current becomes smaller than drained by the load resistor, capacitor starts a discharge to supply it. At the end of a period,  $Q_1$  is "on" and the cycle is restarted. The time in which  $Q_1$  is "on" or "off" is controlled by PWM.

Figure 2.1. Buck converter topology.

#### 2.2.1 Conduction modes of Buck Converter

According to inductor current variation, buck converter can present three different conduction modes: continuous, discontinuous and critical conduction [53], [54].

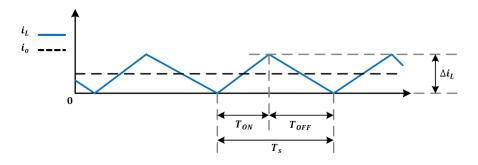

In continuous conduction mode, Buck Converter assumes two states per switching cycle. First, ON state is when  $Q_1$  is "on" and  $D_1$  is "off", inductor current,  $i_L$ , flows from the input source,  $V_i$ , through  $Q_1$  and to output capacitor and load resistor combination. During the ON state, the voltage applied across the inductor is constant and increases linearly. Second,

OFF state is when  $Q_1$  is "off" and  $D_1$  is "on". During the OFF state, the magnitude of the voltage applied across the inductor is constant. Maintaining the same polarity convention, this applied voltage is negative (or opposite in polarity from the applied voltage during the ON time). Hence, the inductor current decreases during the OFF time. A simple linear circuit can represent each of the two states where the switches in the circuit are replaced by their equivalent circuits during each state. The circuit diagram for each of the two states is shown in Fig. 2.2. The increase and decrease in inductor current, during  $T_{ON}$  and  $T_{OFF}$  respectively, are illustrated in Fig. 2.3.

Figure 2.2. Buck Power Stage States.

The ON state duration is  $D = \frac{T_{ON}}{T_S}$  where D is the duty cycle, set by the control circuit, expressed as a ratio of the switch ON time to the time of one complete switching cycle,  $T_S$ . The OFF state duration is called  $T_{OFF}$  where  $T_{OFF} = (1 - D)T_S$ , D' = (1 - D). Since there are only two states per switching cycle for continuous mode. These times are shown along with the waveforms in Fig. 2.3.

Figure 2.3. Typical waveforms for Buck Power Stage States.

In Discontinuous Conduction Mode (DCM), inductor current is zero for a portion of switching cycle due to the reduction of the load current below the critical current level. In a (nonsynchronous) buck power stage, if the inductor current attempts to fall below zero, it just stops at zero (due to the unidirectional current flow in  $D_1$ ) and remains there until the beginning of the next switching cycle. A power stage operating in discontinuous conduction mode has three unique states during each switching cycle as opposed to two states for continuous conduction mode. The load current condition where the power stage is at the boundary between continuous and discontinuous mode is shown in Fig. 2.4. This is where the inductor current falls to zero and the next switching cycle begins immediately after the current reaches zero.

Figure 2.4. Boundary between Continuous and Discontinuous Mode.

Further reduction in output load current puts the power stage into discontinuous conduction mode. This condition is illustrated in Fig. 2.5.

Figure 2.5. Discontinuous Current Mode.

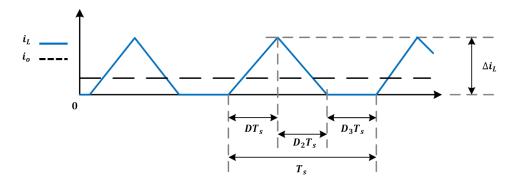

The power stage assumes three unique states during discontinuous current mode operation. First, ON state is when  $Q_1$  is "on" and  $D_1$  is "off". Second, OFF state is when  $Q_1$  is "off" and  $D_1$  is "on". And finally, IDLE state that is when both  $Q_1$  and  $D_1$  are "off". The first two states are identical to those of the continuous mode case and the circuits of Fig. 2.2 are applicable except that  $T_{OFF} \neq (1-D)T_s$ . The remainder of the switching cycle is the IDLE state. In addition, dc resistance of the output inductor, output diode forward voltage drop, and power MOSFET ON-state voltage drop are all assumed to be small enough to omit.

ON state duration is  $DT_s = T_{ON}$ , where D is the duty cycle, set by the control circuit, expressed as a ratio of the switch ON time to the time of one complete switching cycle,  $T_s$ . OFF state duration is  $T_{OFF} = D_2 T_s$ . The IDLE time is the remainder of the switching cycle and is given as  $D_3 T_s = T_s - T_{ON} - T_{OFF}$ . These times are shown with the waveforms in Fig. 2.6.

Figure 2.6. Discontinuous-Mode Buck Power Stage Waveforms.

where  $i_{pk}$  is the peak inductor current.

It should be noted that the buck power stage is rarely operated in discontinuous conduction mode in normal situations, but discontinuous conduction mode will occur anytime the load current is below the critical level.

In critical conduction mode, inductor current reaches the zero value at the exact moment of a new switching cycle, immediately increasing again. Thus, a buck power stage can be designed to operate in continuous mode for load currents above a certain level usually 5% to 10% of full load. Usually, the input voltage range, the output voltage and load current are defined by the power stage specification. This leaves the inductor value as the design parameter to maintain continuous conduction mode [54].

#### 2.2.2 Dynamic of Buck Converter

As shown in Fig. 2.1, the model of buck converter in Continuous Conduction Mode (CCM) can be written as follows:

$$\begin{cases} L\frac{di_L(t)}{dt} = d(t)V_i - v_c(t) - r_L i_L(t) \\ C\frac{dv_c(t)}{dt} = i_L(t) - \frac{v_c(t)}{R_L} \end{cases}$$

(2.1)

Considering the presence of energy storage elements in the circuit, the system modeling must be based on the differential equations that determine the behavior of its state variables, the voltage in the capacitor  $(v_c)$  and the current in the inductor  $(i_L)$ , and its organization in state equations [55], and (d(t)) is the duty cycle. Due to the non-linearity introduced by static switching, the analysis can be divided into two different operation intervals for each period as discussed above in the continuous operation mode. Therefore, ON stage, when  $0 \le t \le T_{ON}$ ,  $i_C(t) = i_L(t) - i_{R_L}(t)$ ,  $v_L(t) = V_i - v_C(t)$ , and d(t) = 1. Thus for the ON stage, state equations are given by equations (2.2) and (2.3).

$$\frac{di_L(t)}{dt}_{ON} = -\frac{r_L}{L}i_L(t) - \frac{1}{L}v_c(t) + \frac{V_i}{L}$$

(2.2)

$$\frac{dv_c(t)}{dt}_{ON} = \frac{1}{C}i_L(t) - \frac{1}{R_L.C}v_c(t)$$

(2.3)

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix}_{ON} = \begin{bmatrix} -\frac{r_L}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{R_L \cdot C} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_i$$

(2.4)

For the OFF stage, when  $T_{ON} \le t \le T_s$ ,  $i_C(t) = i_L(t) - i_R(t)$ ,  $v_L(t) = -v_C(t)$ , and d(t) = 0. The state equations that represent this stage are shown below,

$$\frac{di_{L}(t)}{dt} = -\frac{r_{L}}{L}i_{L}(t) - \frac{1}{L}v_{c}(t)$$

(2.5)

$$\frac{dv_c(t)}{dt}_{OFF} = \frac{1}{C}i_L(t) - \frac{1}{R_L C}v_c(t)$$

(2.6)

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix}_{OFF} = \begin{bmatrix} -\frac{r_L}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{R_L \cdot C} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \end{bmatrix} V_i$$

(2.7)

Equations (2.4) and (2.7) represent the mathematical model in the state space of the buck converter in CCM. Therefore, the dynamic behavior of the converter can be approximated by a switching cycle as shown in equations (2.8) and (2.9),

$$T_{s} \cdot \begin{bmatrix} \frac{di_{L}}{dt} \\ \frac{dv_{c}}{dt} \end{bmatrix} = d(t) \cdot T_{s} \cdot \begin{bmatrix} \frac{di_{L}}{dt} \\ \frac{dv_{c}}{dt} \end{bmatrix} + [1 - d(t)] \cdot T_{s} \cdot \begin{bmatrix} \frac{di_{L}}{dt} \\ \frac{dv_{c}}{dt} \end{bmatrix}$$

(2.8)

$$\begin{bmatrix} \frac{di_L(t)}{dt} \\ \frac{dv_c(t)}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{r_L}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{R_L \cdot C} \end{bmatrix} \begin{bmatrix} i_L(t) \\ v_c(t) \end{bmatrix} + \begin{bmatrix} \frac{V_i}{L} \\ 0 \end{bmatrix} d(t)$$

(2.9)

Considering the practical interest of controlling the converter output by switching applied to gate of power transistor and defining the capacitor voltage as output of the system, y(t), the transfer function for voltage control, described in (2.12), can be calculated by equation (2.11).

$$y(t) = \begin{bmatrix} 0 & 1 \end{bmatrix} \begin{bmatrix} i_L(t) \\ v_c(t) \end{bmatrix}$$

(2.10)

$$\frac{V_c(s)}{D(s)} = C \cdot (sI - A)^{-1} \cdot B + D \tag{2.11}$$

$$\frac{V_c(s)}{D(s)} = \frac{\frac{V_i}{LC}}{s^2 + \left(\frac{1}{R_L \cdot C} + \frac{r_L}{L}\right)s + \left(\frac{1}{LC} + \frac{r_L}{R_L \cdot L \cdot C}\right)}$$

(2.12)

#### 2.3 CASCADED DC-DC BUCK CONVERTER SYSTEM

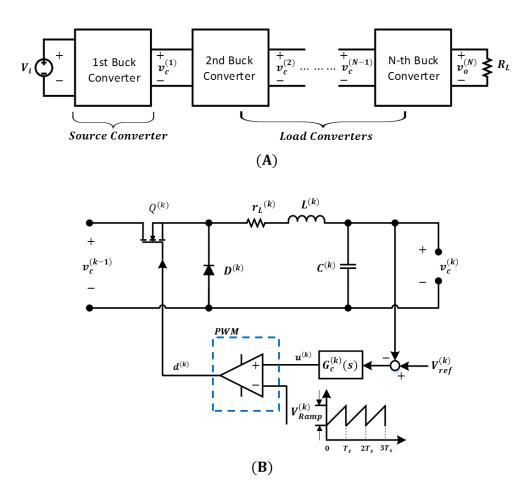

A multi-converter system comprised of cascaded converters have a basic configuration that consists of two or more converters in series connection, where the first is a source converter that maintains a regulated dc voltage on the intermediate bus while remaining are load converters that convert the intermediate bus voltage to tightly regulated outputs for the next system stage or load. In a cascaded buck converter system a large variety of dynamic and static interactions are possible and these can lead to irregular behavior of a converter, a group of converters or the whole system. A typical cascaded system with *N* DC–DC buck converters is shown in Fig. 2.7(A). Fig. 2.7(B) shows a generic configuration for voltage control for the k-th converter.

Figure 2.7. Buck Converter system in series connection: (A) Cascaded system with N-converter.

(B) Voltage mode control for the k-th converter.

As mentioned earlier, when a load converter is tightly regulated and its switching operation frequency is faster than source converter, load converter behavior will be as a CPL. As a result, in CPL, input current increases when input voltage decreases, and vice versa. CPL approximation model describe the behavior at the input terminals of the load converter allows to capture its performance in a frequency range where its open-loop gain is high and an input voltage span where its controller is within its dynamic range.

#### 2.3.1 Buck Converter with constant power load

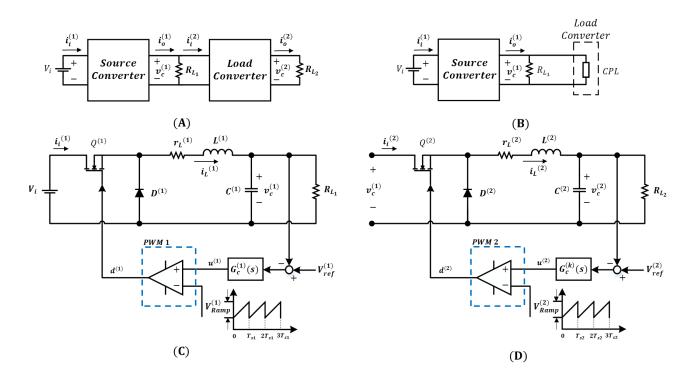

Cascaded buck converter system and its representation with CPL are shown in Figs. 7.8(A) and 7.8(B), respectively. Source and load converter are in voltage control mode as shown in Figs. 7.8(C) and 7.8(D).

Figure 2.8. Cascaded buck converter with two power stages. (A) Diagram of the cascaded converters. (B) Source converter loaded by a CPL. (C) Voltage mode control for source converter. (D) Tight regulated load converter.

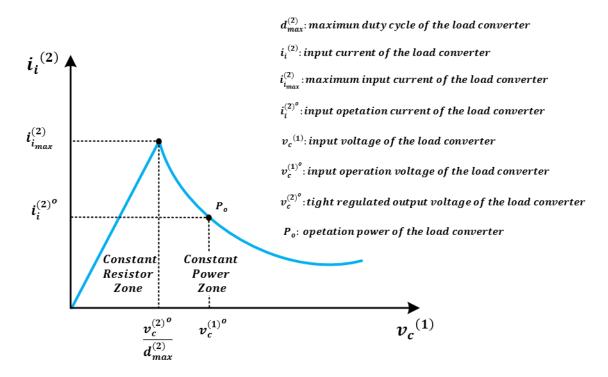

CPLs introduce interesting nonlinear behavior to conventional buck-converter dynamics but this behavior only exhibit above a certain voltage (see Fig. 2.9). Fig. 2.9 shows the input "V-I" characteristics of load converter. When the input voltage of the load converter,  $v_c^{(1)}$ , is

lower than  $\binom{v_c^{(2)}}{d_{max}^{(2)}}$ , the load converter behavior will be as the resistive load. Therefore, in this range of operation, load converter will be operate in a constant resistor zone (CRZ). On the other hand, when  $v_c^{(1)}$  is higher than  $\binom{v_c^{(2)}}{d_{max}^{(2)}}$ , the load converter behavior will be as a CPL, thus, load converter will be operate in a constant power zone (CPZ).

Figure 2.9. Input "V -I" characteristics of the CPL.

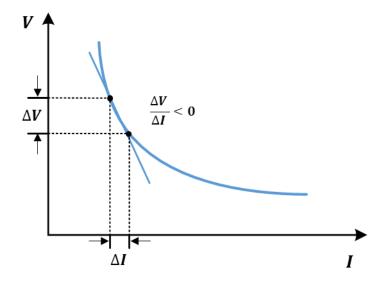

For a CPL, in order to maintain a constant power level, in load converter, input current increases when input voltage decreases, and vice versa, so the product of the input current and input voltage of the load converter (i. e.,  $P_o = i_i^{(2)} v_c^{(2)}$ ) is a constant and the instantaneous value of the load impedance is positive (i. e.,  $v_c^{(2)}/i_i^{(2)} > 0$ ). However, the incremental impedance is always negative (i.e.,  $\Delta V/\Delta I < 0$ ) due to once appearing any disturbance, thus operating point will leave from previous point and never return. This negative incremental

impedance has a negative impact on the power quality and stability of the system. The curve, in Fig. 2.10, shows the negative incremental impedance behavior of CPL.

Figure 2.10. The negative incremental impedance behavior of CPL.

## 2.3.2 Instability in a DC-DC Buck Converter with constant power load

The system (see Fig. 8(B)) is used to show the instability of a dc-dc converter with a constant power load. To obtain the large-signal behavior of the load converter, the CPL is represented by a dependent current source,  $i_{CPL}(t) = \frac{P_0}{v_c^{(1)}(t)}$ , so the total instantaneous current drawn from source converter is given by

$$i_o^{(1)}(t) = \frac{v_c^{(1)}(t)}{R_{L_1}} + \frac{P_o}{v_c^{(1)}(t)}$$

(2.13)

$$i_o^{(1)}(t) = i_{R_{L_1}}(t) + i_{CPL}(t)$$

(2.14)

where,  $P_o$  in the output power of the converter that is constant.

Depending on switching of the source converter, the large-signal model of the converter in CCM can be obtained based on the following equations:

$$\begin{cases}

\frac{di_L^{(1)}(t)}{dt} = -\frac{r_L^{(1)}}{L^{(1)}}i_L^{(1)}(t) + \frac{1}{L^{(1)}}\left(V_i - v_c^{(1)}(t)\right) \\

\frac{dv_c^{(1)}(t)}{dt} = \frac{1}{C^{(1)}}i_L^{(1)}(t) - \frac{1}{C^{(1)}}\left(\frac{v_o^{(1)}(t)}{R_{L_1}} + \frac{P_o}{v_c^{(1)}(t)}\right)

\end{cases}$$

When  $0 < t < d^{(1)}T_{s_1}$  (2.15)

$$\begin{cases} \frac{di_L^{(1)}(t)}{dt} = -\frac{r_L^{(1)}}{L^{(1)}}i_L^{(1)}(t) + \frac{1}{L}\left(-v_c^{(1)}(t)\right) \\ \frac{dv_c^{(1)}(t)}{dt} = \frac{1}{C^{(1)}}i_L^{(1)} - \frac{1}{C^{(1)}}\left(\frac{v_c^{(1)}(t)}{R_{L_1}} + \frac{P_o}{v_c^{(1)}(t)}\right) \end{cases}$$

When  $d^{(1)}T_{s_1} < t < T_{s_1}$  (2.16)

where  $d^{(1)}$  and  $T_{s_1}$  are the duty cycle and switching period of the source converter, respectively. Using the state-space averaging method [14], [40], [41], the buck converter dynamic can be written as

$$\begin{cases}

\frac{di_L^{(1)}(t)}{dt} = -\frac{r_L^{(1)}}{L^{(1)}}i_L^{(1)}(t) + \frac{1}{L^{(1)}}\left(V_i \cdot d^{(1)} - v_c^{(1)}(t)\right) \\

\frac{dv_c^{(1)}(t)}{dt} = \frac{1}{C^{(1)}}i_L^{(1)}(t) - \frac{1}{C^{(1)}}\left(\frac{v_c^{(1)}(t)}{R_{L_1}} + \frac{P_o}{v_c^{(1)}(t)}\right)

\end{cases} (2.17)$$

Consider small perturbations in the state variables due to small disturbances in the input voltage and duty cycle

$$\begin{cases} V_{i} = \bar{V}_{i} + \tilde{V}_{i} \\ d^{(1)} = D^{(1)} + \tilde{d}^{(1)} \\ v_{c}^{(1)} = V_{c}^{(1)} + \tilde{v}_{c}^{(1)} \\ i_{L}^{(1)} = I_{L}^{(1)} + \tilde{i}_{L}^{(1)} \end{cases}$$

(2.18)

where,  $\bar{V}_i$ ,  $D^{(1)}$ ,  $V_c^{(1)}$ , and  $I_L^{(1)}$  are the average values of  $V_i$ ,  $d^{(1)}$ ,  $v_c^{(1)}$  and  $i_L^{(1)}$ , respectively. Substituting (2.18) in (2.17) and neglecting the internal resistance of the inductor to simplify the calculations, the buck converter dynamic becomes

$$\begin{cases}

\frac{d\tilde{\imath}_{L}^{(1)}}{dt} = \frac{1}{L^{(1)}} \left( \bar{V}_{i} \cdot \tilde{d}^{(1)} + D^{(1)} \tilde{V}_{i} - \tilde{\nu}_{c}^{(1)} \right) \\

\frac{d\tilde{\nu}_{c}^{(1)}}{dt} = \frac{1}{C^{(1)}} \left( \tilde{\imath}_{L}^{(1)}(t) - \frac{P_{o} \tilde{\nu}_{c}^{(1)}}{V_{c}^{2}} \right)

\end{cases} (2.18)$$

Note that the following approximation was made in (2.18),  $\bar{V}_i \gg \tilde{V}_i$  and  $V_c^{(1)} \gg \tilde{v}_c^{(1)}$ .

The transfer functions of the system can be obtained from (2.18) as follows:

$$\begin{cases} G_{1}(s) = \frac{\tilde{v}_{c}^{(1)}(s)}{\tilde{d}^{(1)}(s)} = \frac{\bar{V}_{i}/LC}{s^{2} - \left(\frac{P_{o}}{CV_{c}^{2}}\right)s + \frac{1}{LC}} \\ G_{2}(s) = \frac{\tilde{v}_{c}^{(1)}(s)}{\tilde{V}_{i}(s)} = \frac{D^{(1)}/LC}{s^{2} - \left(\frac{P_{o}}{CV_{c}^{2}}\right)s + \frac{1}{LC}} \end{cases}$$

(2.19)

Due to CPL, the transfer functions in (2.19) have poles in the right half plane, thus, the system is unstable.

Linear controllers can be designed to stabilize the system around a specific operating point based on a linearized small-signal model, such as that described in (2.19). However, when the operating point (i.e., the input voltage  $V_i$  or the load power  $P_o$ ) significantly changes, the system, which still contains unstable poles, may not be able to be stabilized by using the same linear controller.

#### 2.4 STABILITY ANALYSIS OF MULTI-CONVERTER BUCK-BUCK SYSTEM

#### 2.4.1 Stability of multi-converter buck-buck system

In order to perform a local stability analysis of the system, the system is constituted operating at a certain operating point, see Table 3.1, which presents the parameters value and the operating point to which the system is linearized.

Table 2.1. Values for the physical parameters of the multi-converter buck-buck system.

| Par.      | Unit  | Val. | Description                                  |  |

|-----------|-------|------|----------------------------------------------|--|

| $V_{C1}$  | V     | 6,0  | Output voltage of source converter (output 1 |  |

| $P_o$     | p. u. | 0,5  | Output power of load converter (output 2)    |  |

| $V_i$     | V     | 15,0 | DC input voltage                             |  |

| $R_{L_1}$ | Ω     | 4,0  | Load Resistance of source converter          |  |

| $R_{L_2}$ | Ω     | 4,0  | Load Resistance of load converter            |  |

| $C_1$     | μF    | 2000 | Capacitor of source converter                |  |

| $C_2$     | μF    | 2200 | Capacitor of load converter                  |  |

| $L_1$     | mH    | 2,0  | Inductance of source converter               |  |

| $L_2$     | mH    | 2,0  | Inductance of load converter                 |  |

| $r_{L_1}$ | Ω     | 0.05 | Internal resistance of $L_1$                 |  |

| $r_{L_2}$ | Ω     | 0.05 | Internal resistance of $L_2$                 |  |

| $D_1$     | %     | 42.4 | Operational point for duty cycle of output   |  |

| $D_2$     | %     | 60.0 | Operational point for duty cycle of output 2 |  |

| $f_{s_1}$ | kHz   | 1.0  | Switching frequency of source converter      |  |

| $f_{s_2}$ | kHz   | 5.0  | Switching frequency of load converter        |  |

| $P_{max}$ | W     | 20.0 | Maximum power                                |  |

All the roots of the characteristic polynomial of the system are obtained to verify if all the roots of system are located in the left half of the imaginary plane. In the case that at least one root is in the right half-plane, the entire system is considered unstable [55], [56], [48]. Table 2.2 shows the eigenvalues of the linearized multi-converter buck-buck system.

Table 2.2. Eigenvalues of the linearized multi-converter buck-buck system.

| Source Converter  |  |  |  |  |  |

|-------------------|--|--|--|--|--|

| -62.50 + i 496.08 |  |  |  |  |  |

| −62.50 − i 496.08 |  |  |  |  |  |

| Load Converter    |  |  |  |  |  |

| -500              |  |  |  |  |  |

| -500              |  |  |  |  |  |

All eigenvalues of the system have a negative real part, thus, the system is stable for this point of operation as shown in Table 2.2.

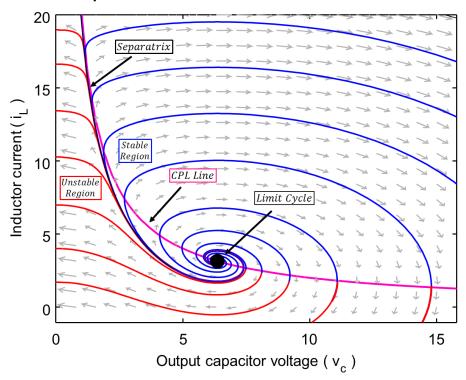

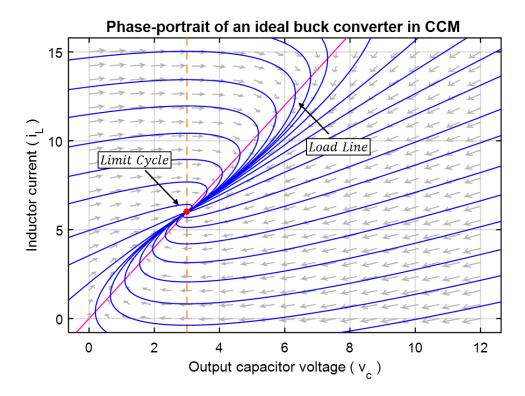

# 2.4.2 Phase-plane analysis of multi-converter buck-buck system

A system can be analyzed by a phase-plane analysis, solving (plotting) the system differential equations giving an insight about how the system dynamics evolve with time [25], [57], [58]. This technique can be used to study global close-loop behavior of the converter feeding a CPL. The phase-portrait of source converter feeding a CPL is shown in Fig. 2.11 with the physical parameters specified in Table 2.1. The pink line is the load line of the CPL; the blue and red lines represent the trajectory of the state variable [ $i_{L1}$   $v_{C1}$ ]; the gray arrow indicates the evolving direction of the trajectory. The state plane is divide into two regions by the separatrix (black line): the left region of the separatrix is an unstable region, and the right region of the separatrix is a stable region. Moreover, when the state variable is in the stable region, the trajectory will converge to a limit cycle. On the other hand, when the state variable is in unstable region, any controller cannot guarantee the converter's stability. The phase-portrait of load converter is shown in Fig. 2.12 checking the non-linearity of load converter.

# Phase-portrait of an ideal buck converter loaded with a CPL

Fig. 2.11. Phase-portrait of source converter loaded with a CPL ( $V_i=15~\mathrm{V}, D_1=0.424,$

CPL Power  $P_o=0.5$  p. u., L=2 mH, C=2000  $\mu F)$ .

Fig. 2.12. Phase-portrait of load converter (Input DC voltage = 6 V,  $D_2 = 0.6$ ,

$$P_o=0.5~\mathrm{p.\,u.}, L=2~\mathrm{mH}, C=2000~\mathrm{\mu F}).$$

# 2.4 CONCLUSION

In this chapter, the mathematical model that describes the behavior of a multi-converter buck-buck system were present, with its operation and behavior characteristics. The instability problem caused by a CPL in a multi-converter system was described. In addition, the system stability analysis was performed with the operating conditions described in this chapter. The robust controller design methodology will be presented in the next chapter.

### CHAPTER 3

# ROBUST PARAMETRIC CONTROL: THEORY AND APPLICATION IN THE DESIGN OF ROBUST CONTROLLERS

#### 3.1 INTRODUCCION

Control systems are usually constituted aiming to attend certain close-loop performance desired characteristics. In general, to meet these desired conditions a set of process variables is forced for obtaining the dynamics behavior previously established, thus complying with certain restrictions such as: zero steady-state error, time and frequency requirements, in order to obtain a good dynamic performance.

The controller design is usually based on a linear approximation of nonlinear dynamics systems. However, conventional controllers may experience a sensible performance deterioration under varying operating conditions [14]. In order to assure robustness against varying operating conditions, linear controllers may be designed by using robust control theory. Robust Parametric Control (RPC) Theory, which emerges as a set of modern control techniques, aiming to avoid the negative effects caused by the uncertainties present in the system parameters [45]. The RPC gained greater attention from academia since the 1980s because of Kharitonov's work, who developed the so-called seminal Kharitonov stability Theorem.

In this chapter, some methodologies, for designing of robust parametric controllers, are presented, taking into account a parametric variation in a certain region of uncertainties previously determined by the designer.

#### 3.2 BRIEF REVIEW OF ROBUST CONTROL THEORY

Mathematical models naturally present errors that are neglected, depending on the type of study. An important consideration in model-based control systems is to keep the system stable, subject to parametric variations. However, generally in the classic controller design, models that ignore uncertainties are used [46]. In this way, it is common to use a nominal transfer function for the controller design. Although the controller is developed based on a nominal transfer function, the real system must be stable for all kinds of transfer functions that represent the whole set of uncertainties. Thereby, uncertainty of a system can be classified as unstructured (non-parametric uncertainty) and structured (parametric uncertainty) [43], [45].

Robust parametric control techniques are useful for stability and control analysis of systems subjected to uncertainties in the parameters of the representative models (structured uncertainty).

#### 3.2.1 Robust Stability Analysis

A system with interval parametric uncertainties is generally described by uncertain interval polynomials B(s) and A(s), restricted within pre-specified closed real intervals, as shown in (3.1) [45].

$$G(s) = \frac{B(s)}{A(s)} = \frac{\sum_{i=0}^{m} \left[ b_i^-, b_i^+ \right] s^i}{\sum_{i=0}^{n} \left[ a_i^-, a_i^+ \right] s^i}$$

(3.1)

Many robust stability tests under parametric uncertainty are based on analysis of uncertain characteristic polynomial assumed as an interval polynomial family [45], such as

$$P(s,p) = \sum_{i=0}^{N} [p_i^-, p_i^+] s^i$$

(3.2)

where  $p = ([p_0^-, p_0^+], [p_1^-, p_1^+], ..., [p_N^-, p_N^+])$  is a vector of interval elements.

Polynomial P(s,p) is stable if all its roots are contained on the left-hand side of the complex plane s-plane. Then, P(s,p) is robustly stable if all its polynomials are stable for a set of operating point different from the nominal operating point within its minimum and maximum limits [49].

Thus, according to [45], two definitions can be defined that characterize the stability concept of the families of polynomials.

**Definition 3.1** (Stability): A fixed polynomial P(s) is stable if all its roots are strictly located in the left half-plane of the complex plane.

**Definition 3.2** (Robust Stability): A certain family of polynomials P(s,p) is robustly stable if P(s,p) is stable for all  $a \in \mathbb{R}$ , i.e., all the roots of P(s,a) are located strictly in the left half-plane of the complex plane.

# 3.2.2 Kharitonov Stability Theorem [43]

The Kharitonov Theorem is a test used in robust control theory to evaluate the stability of a dynamic system whose parameters vary within a closed real interval as follows:

$$\delta(s) = \delta_0 + \delta_1 s + \delta_2 s^2 + \delta_3 s^3 + \dots + \delta_n s^n$$

(3.3)

where, the coefficient vector  $\overline{\delta} = [\delta_0, \delta_1, \delta_2, \delta_3, \cdots, \delta_n]$  is delimited by:

$$\Delta = \left[ \delta_0^-, \delta_0^+ \right] \times \left[ \delta_1^-, \delta_1^+ \right] \times \dots \times \left[ \delta_n^-, \delta_n^+ \right]$$

(3.4)

where,  $\delta_n^-$  and  $\delta_n^+$  represent the lower and upper limit respectively. Therefore, the Kharitonov polynomials are defined as:

$$K_{1}(s) = \delta_{0}^{-} + \delta_{1}^{-} s + \delta_{2}^{+} s^{2} + \delta_{3}^{+} s^{3} + \delta_{4}^{-} s^{4} + \delta_{5}^{-} s^{5} + \delta_{6}^{+} s^{6} + \cdots$$

$$K_{2}(s) = \delta_{0}^{-} + \delta_{1}^{+} s + \delta_{2}^{+} s^{2} + \delta_{3}^{-} s^{3} + \delta_{4}^{-} s^{4} + \delta_{5}^{+} s^{5} + \delta_{6}^{+} s^{6} + \cdots$$

$$K_{3}(s) = \delta_{0}^{+} + \delta_{1}^{-} s + \delta_{2}^{-} s^{2} + \delta_{3}^{+} s^{3} + \delta_{4}^{+} s^{4} + \delta_{5}^{-} s^{5} + \delta_{6}^{-} s^{6} + \cdots$$

$$K_{4}(s) = \delta_{0}^{+} + \delta_{1}^{+} s + \delta_{2}^{-} s^{2} + \delta_{3}^{-} s^{3} + \delta_{4}^{+} s^{4} + \delta_{5}^{+} s^{5} + \delta_{6}^{-} s^{6} + \cdots$$

$$(3.5)$$

**Theorem 3.1** (Robust Stability): The interval polynomial family delimited by  $\Delta$  is robustly stable if and only if its four Kharitonov polynomials are stable [45], [59], i.e., all roots of the interval polynomial are in the left hand-plane of the complex plane.

#### 3.3 SISO ROBUST CONTROLLER DESIGN VIA INTERVAL POLE-PLACEMENT

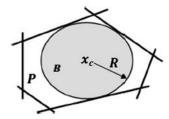

To design the controller, a region of uncertainty is previously defined, considering that the uncertainty is contained in the parameter variation of the plant-model. The robust controller design uses two different procedures considering the closed-loop control system in Fig. 3.1. The first is the tool developed in [46], associated with a linear goal programming formulation, which will lead to a set linear inequality constraints. The second procedure is the Chebyshev theorem, developed in [47], which provides a maximum stability region, characterized by a ball of center  $x_c$  and radium R, whose norm is Euclidean.

Figure 3.1. Closed-loop system block-diagram.

where G(s,p) is the uncertain plant of order n and C(s,x) is the controller of order r, defined in (3.5) and (3.6) respectively. Note that  $a_i$  and  $b_i$  define the box region of uncertainties denoted by  $a_i^- \le a_i \le a_i^+$  and  $b_j^- \le b_j \le b_j^+$  for  $i=1,2,\ldots,n$ ;  $j=1,2,\ldots,m$ .

$$G(s,p) = \frac{n(s)}{d(s)} = \frac{b_1 s^{m-1} + \dots + b_{m-1} s + b_m}{s^n + a_1 s^{n-1} + \dots + a_{n-1} s + a_n}$$

(3.5)

$$C(s) = \frac{n_c(s)}{d_c(s)} = \frac{x_0 s^r + x_1 s^{r-1} + \dots + x_{r-1} s + x_r}{s^r + y_1 s^{r-1} + \dots + y_{r-1} s + y_r}$$

(3.6)

Let p be the vector of parameters that represent the plant and x the vector of real parameters representing the controller defined in (3.7) and (3.8) respectively. In addition,  $p^o$  represents the nominal value of plant parameters defined in a box region of uncertainties.

$$p := [b_1 \quad b_2 \quad \cdots \quad b_{m-1} \quad b_n \quad a_1 \quad a_2 \quad \cdots \quad a_{n-1} \quad a_n]$$

(3.7)

$$X := \begin{bmatrix} x_0 & x_1 & \cdots & x_{r-1} & x_r & y_1 & y_2 & \cdots & y_{r-1} & y_r \end{bmatrix}$$

(3.8)

According to [60], [61], the solution of the Diophantine equation (3.9) summarizes the pole-placement problem.

$$d(s) = d(s)d_{s}(s) + n(s)n_{s}(s)$$

(3.9)

where d(s) is the closed-loop characteristic polynomial. Therefore, the parameters of the closed-loop characteristic polynomial are represented as follows:

$$d_i = d_i(x, p) \tag{3.10}$$

Assuming that the desired dynamic of closed-loop system is represented by

$$\Delta_{d}(s) = s^{i} + \phi_{i}s^{i-1} + \dots + \phi_{i-1}s + \phi_{i}$$

(3.11)

where  $\phi_i$  represent the parameters of the closed-loop desired polynomial.

Aiming of tuning the controller, the closed-loop parameters obtained are compared with the parameters of the closed-loop desired polynomial, which represent the desired dynamics of the system as a result Eq. (3.12).

$$d_i(x, p^o) = \phi_i, \quad i = 1, 2, ..., l$$

(3.12)

This problem can be written in its matrix format, presenting the following relationship:

$$\begin{bmatrix} [b_{1}] & 0 & \cdots & 0 & 0 & | & 1 & 0 & \cdots & 0 & 0 \\ [b_{2}] & [b_{1}] & \ddots & \vdots & 0 & | & [a_{1}] & 1 & \ddots & \vdots & 0 \\ \vdots & [b_{2}] & \ddots & 0 & \vdots & | & \vdots & [a_{1}] & \ddots & 0 & \vdots \\ [b_{m-1}] & \vdots & \ddots & [b_{1}] & 0 & | & [a_{n-1}] & \vdots & \ddots & 1 & 0 \\ [b_{m}] & [b_{m-1}] & \ddots & [b_{2}] & [b_{1}] & | & [a_{n}] & [a_{n-1}] & \ddots & [a_{1}] & 1 \\ 0 & [b_{m}] & \ddots & \vdots & [b_{2}] & | & 0 & [a_{n}] & \ddots & \vdots & [a_{1}] \\ \vdots & 0 & \ddots & [b_{m-1}] & \vdots & | & \vdots & 0 & \ddots & [a_{n-1}] & \vdots \\ 0 & \vdots & \ddots & [b_{m}] & [b_{m-1}] & | & 0 & \vdots & \ddots & [a_{n}] & [a_{n-1}] \\ 0 & 0 & \cdots & 0 & [b_{m}] & | & 0 & 0 & \cdots & 0 & [a_{n}] \end{bmatrix} \underbrace{ \begin{bmatrix} x_{0} \\ x_{1} \\ \vdots \\ x_{r-1} \\ x_{r} \\ - \\ y_{0} \\ y_{1} \\ \vdots \\ y_{r-1} \\ y_{r} \end{bmatrix} }_{B}$$

$$(3.13)$$

When the system is subject to parametric uncertainties, the controller performance may deteriorate. Therefore, the controller must guarantee robust performance within an acceptable region of closed-loop parameters variation, so that the closed-loop poles are located in a certain region. Thereby, a desired region is defined as follows:

$$\Phi := \left\{ \phi_i^- \le \phi_i \le \phi_i^+ \right\} \tag{3.14}$$

Therefore, according to [49], replacing the parameters of equation (3.14) in equation (3.12), it is possible to formulate a linear inequalities set, which restricted the controller and desired polynomial coefficients in the predefined intervals, as shown in Eq. (3.15). Thus, the closed-loop system has its poles within the roots space of interval-desired polynomial, ensuring the robust stability [60].

$$\phi_i^- \le d_i(x, p) \le \phi_i^+, \quad i = 1, 2, ..., l$$

(3.15)

The condition in Eq. (3.15) can be illustrated by Eq. (3.16), assuring stability and performance requirements [60].

$$\Re(d(s)) \subseteq \Re(\Delta_d(s)) \tag{3.16}$$

where  $\Re(d(s))$  denotes the roots space or polynomial poles of d(s) and  $\Re(\Delta_d(s))$  denotes the roots space of desired polynomial family  $\Delta_d(s)$ .

The solution of this problem can be idealized, as a solution to a linear programming problem, therefore different techniques can be used to solve it. However, its standard solution is sometimes efficient and fast, so that this problem can be rewritten as a problem of local minimization, subject to restrictions, according to relations defined in [46], [43], [45] [39], [40], and [41].

#### 3.3.1 Linear Programing based on Kharitonov's Rectangle

The coefficients of vector X can be calculated by using the linear programming technique as shown below [49],

$$X = \arg\left(\min \ f(X)\right)$$

$$s.t. \begin{bmatrix} A_{upper} \\ -A_{lower} \end{bmatrix} X \le \begin{bmatrix} B(\phi^{+}) \\ -B(\phi^{-}) \end{bmatrix}$$

(3.17)

where,