# ESTRATÉGIAS DE PARALELISMO COM GPGPU PARA OTIMIZAÇÃO DO PROCESSAMENTO DO CÁLCULO DO FLUXO DE CARGA EM SISTEMAS ELÉTRICOS DE POTÊNCIA

IGOR MEIRELES DE ARAÚJO

DM:15/2017

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil **2017**

IGOR MEIRELES DE ARAÚJO

ESTRATÉGIAS DE PARALELISMO COM GPGPU PARA OTIMIZAÇÃO DO PROCESSAMENTO DO CÁLCULO DO FLUXO DE CARGA EM SISTEMAS ELÉTRICOS DE POTÊNCIA

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil **2017**

#### IGOR MEIRELES DE ARAÚJO

## ESTRATÉGIAS DE PARALELISMO COM GPGPU PARA OTIMIZAÇÃO DO PROCESSAMENTO DO CÁLCULO DO FLUXO DE CARGA EM SISTEMAS ELÉTRICOS DE POTÊNCIA

Dissertação submetida à Banca Examinadora do Programa de Pós-graduação em Engenharia Elétrica da UFPA para a obtenção do Grau de Mestre em Engenharia Elétrica na área de Computação Aplicada, elaborada sob a orientação do Prof. Dr. Ádamo Lima de Santana.

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil **2017**

## ESTRATÉGIAS DE PARALELISMO COM GPGPU PARA OTIMIZAÇÃO DO PROCESSAMENTO DO CÁLCULO DO FLUXO DE CARGA EM SISTEMAS ELÉTRICOS DE POTÊNCIA

AUTOR: IGOR MEIRELES DE ARAÚJO

| DISSERTAÇÃO DE MESTRADO SUBMETIDA À AVALIAÇÃO DA BANCA<br>EXAMINADORA APROVADA PELO COLEGIADO DO PROGRAMA DE PÓS-<br>GRADUAÇÃO EM ENGENHARIA ELÉTRICA DA UNIVERSIDADE FEDERAL DO PARÁ<br>E JULGADDA ADEQUADA PARA OBTENÇÃO DO GRAU DE MESTRE EM<br>ENGENHARIA ELÉTRICA NA ÁREA DE COMPUTAÇÃO APLICADA.<br>APROVADA EM// |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BANCA EXAMINADORA:                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                         |

| Prof. Dr. Ádamo Lima de Santana                                                                                                                                                                                                                                                                                         |

| (ORIENTADOR – UFPA)                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                         |

| Prof. Dr. Josivaldo de Souza Araújo                                                                                                                                                                                                                                                                                     |

| (MEMBRO EXTERNO – UFPA-PPGCC)                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                         |

| Prof. Dr. Diego Lisboa Cardoso                                                                                                                                                                                                                                                                                          |

| (MEMBRO INTERNO– UFPA-PPGEE)                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                         |

| VISTO:                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                         |

**Prof. Dr. Evaldo Gonçalves Pelaes** (COORDENADOR DO PPGEE/ITEC/UFPA)

#### **AGRADECIMENTOS**

Primeiramente, agradeço a Deus por todas as oportunidades a mim dadas e principalmente pela minha saúde e a de meus familiares, pois unidos podemos superar os obstáculos impostos pela vida. Obstáculos estes que foram impostos desde meu nascimento, mas que com a fé de todos ao meu redor foram superados.

Agradeço aos meus pais e aos meus irmãos e familiares que confiaram em mim e acreditaram na minha capacidade, me deram suporte e condições de chegar aonde eu cheguei hoje. Também agradeço a minha amiga, companheira e namorada Thamna Maíra, que também me ajudou a enfrentar as dificuldades impostas e compreendeu a importância que este trabalho possui para mim.

Agradeço ao meu orientador, Prof. Dr. Ádamo Lima de Santana, que o considero como um pai no meio acadêmico, pois me acolheu, orientou, enxergou minhas dificuldades e me mostrou o caminho para chegar onde estou hoje, sempre acreditando em mim.

Agradeço aos meus amigos Iago Cavalcante, Gabriel Viana, Alison Rejo e Tiago Rodrigues que desde o início do ensino superior estiveram comigo, cada um apoiando o outro.

Agradeço aos meus colegas de trabalho do LINC que estiveram comigo desde o início desta jornada e aqueles que encontrei ao longo do caminho e, em especial, ao Prof. Dr. Fábio Manoel França Lobato, que também me auxiliou e contribuiu para a realização das minhas conquistas.

Por último, mas não menos importante, agradeço à banca examinadora desta Dissertação de Mestrado, os Professores Dr. Diego Lisboa Cardoso e Dr. Josivaldo de Souza Araújo, que aceitaram em avaliar este trabalho e contribuir para sua excelência. Também a fundação CAPES, a Universidade Federal do Pará e seu Programa e Pós-Graduação em Engenharia Elétrica.

## SUMÁRIO

| LI                             | STA DE     | FI(                                              | GURAS                                                   | VIII |  |  |  |  |

|--------------------------------|------------|--------------------------------------------------|---------------------------------------------------------|------|--|--|--|--|

| LI                             | STA DE     | TA                                               | BELAS                                                   | IX   |  |  |  |  |

| LISTA DE ABREVIATURAS E SIGLAS |            |                                                  |                                                         |      |  |  |  |  |

| RI                             | RESUMOX    |                                                  |                                                         |      |  |  |  |  |

| Al                             | BSTRAC     | Т                                                |                                                         | XII  |  |  |  |  |

| 1                              | INTRODUÇÃO |                                                  |                                                         | 13   |  |  |  |  |

|                                | 1.1 MO     |                                                  | OTIVAÇÃO E DESCRIÇÃO GERAL DO PROBLEMA                  |      |  |  |  |  |

|                                | 1.2        | PR                                               | OBLEMÁTICAS E LIMITAÇÕES ATUAIS                         | 14   |  |  |  |  |

|                                | 1.3        | OB                                               | JETIVOS GERAIS                                          | 15   |  |  |  |  |

|                                | 1.4        |                                                  | BJETIVOS ESPECÍFICOS                                    |      |  |  |  |  |

|                                | 1.5        | ES'                                              | TRUTURA DA DISSERTAÇÃO                                  | 16   |  |  |  |  |

| 2                              | SISTE      | MA                                               | S ELÉTRICOS DE POTÊNCIA                                 | 18   |  |  |  |  |

|                                | 2.1        | CC                                               | NSIDERAÇÕES INICIAIS                                    | 18   |  |  |  |  |

|                                | 2.2        |                                                  | TRUTURA DE UM SISTEMA ELÉTRICO DE POTÊNCIA              |      |  |  |  |  |

|                                | 2.3        | REPRESENTAÇÃO DE UM SISTEMA ELÉTRICO DE POTÊNCIA |                                                         | 20   |  |  |  |  |

|                                | 2.4        | EQ                                               | UIPAMENTOS DE CONTROLE EM SISTEMAS ELÉTRICOS DE POTÊ    |      |  |  |  |  |

|                                | 2.         | .4.1                                             | Regulador Automático de Tensão                          |      |  |  |  |  |

|                                | 2.         | .4.2                                             | Transformador com Tap Variável                          | 22   |  |  |  |  |

|                                | 2.         | .4.3                                             | Compensador Estático Fixo                               | 23   |  |  |  |  |

|                                | 2.5        | FL                                               | UXO DE CARGA                                            | 24   |  |  |  |  |

|                                | 2.         | .5.1                                             | Matriz de Admitância                                    | 24   |  |  |  |  |

|                                | 2.         | .5.2                                             | Modelagem do Fluxo de Carga                             | 25   |  |  |  |  |

|                                | 2.         | .5.3                                             | Solução do Fluxo de Carga pelo Método de Newton-Raphson |      |  |  |  |  |

|                                | 2.6        | PA                                               | RALELISMO DO FLUXO DE CARGA                             | 30   |  |  |  |  |

|                                | 2.7        | CC                                               | ONSIDERAÇÕES FINAIS                                     | 31   |  |  |  |  |

| 3                              | COMP       | UT.                                              | AÇÃO PARALELA EM GPU                                    | 32   |  |  |  |  |

|                                | 3.1        | CC                                               | ONSIDERAÇÕES INICIAIS                                   | 32   |  |  |  |  |

|                                | 3.2        | CC                                               | NTEXTO HISTÓRICO                                        | 32   |  |  |  |  |

|    | 3.3                                          | PL.         | ATAFORMA CUDA                                      | 33 |

|----|----------------------------------------------|-------------|----------------------------------------------------|----|

|    | 3.                                           | 3.1         | Principais definições                              | 33 |

|    | 3.                                           | 3.2         | Arquitetura do Hardware                            | 36 |

|    | 3.                                           | .3.3        | Escalabilidade da Plataforma                       | 38 |

|    | 3.                                           | 3.4         | Paralelismo Dinâmico CUDA                          | 39 |

|    | 3.4                                          | ΜÉ          | ÉTRICAS DE AVALIAÇÃO                               | 40 |

|    | 3.5                                          | CO          | NSIDERAÇÕES FINAIS                                 | 41 |

| 4  | TRABA                                        | <b>AL</b> F | HOS CORRELATOS                                     | 42 |

|    | 4.1                                          | CO          | NSIDERAÇÕES INICIAIS                               | 42 |

|    | 4.2                                          |             | UXO DE CARGA                                       |    |

|    | 4.3                                          | PA          | RALELIZAÇÃO DO FLUXO DE CARGA                      | 43 |

|    | 4.4                                          | FL          | UXO DE CARGA EM GPU                                | 44 |

|    | 4.5                                          | CO          | NSIDERAÇÕES FINAIS                                 | 47 |

| 5  | ESTRATÉGIAS DE PARALELISMO DO FLUXO DE CARGA |             |                                                    |    |

|    | 5.1                                          | CO          | NSIDERAÇÕES INICIAIS                               | 48 |

|    | 5.2                                          | BA          | SE DE DADOS DOS TESTES E CONFIGURAÇÕES DE HARDWARE | 48 |

|    | 5.3                                          | VE          | RSÃO SEQUENCIAL                                    | 49 |

|    | 5.4                                          | VE          | RSÃO TOTALMENTE PARALELIZADA ESPARSA               | 53 |

|    | 5.5                                          | VE          | RSÃO TOTALMENTE PARALELIZADA DENSA                 | 56 |

|    | 5.6                                          | VE          | RSÃO HÍBRIDA PARALELIZADA                          | 57 |

|    | 5.7                                          | VE          | RSÃO COM PARALELISMO DINÂMICO CUDA                 | 59 |

|    | 5.8                                          | CO          | NSIDERAÇÕES FINAIS                                 | 61 |

| 6  | TESTES E RESULTADOS                          |             |                                                    |    |

|    | 6.1                                          | CO          | NSIDERAÇÕES INICIAIS                               | 62 |

|    | 6.2                                          | RE          | SULTADOS                                           | 62 |

|    | 6.3                                          | CO          | NSIDERAÇÕES FINAIS                                 | 67 |

| 7  | CONC                                         | LUS         | SÃO                                                | 68 |

| Βī | EFERÊN                                       | CIA         | A.C.                                               | 71 |

## LISTA DE FIGURAS

| FIGURA 2.1 - ILUSTRAÇÃO DE UM SISTEMA ELÉTRICO DE POTÊNCIA                            | 19       |

|---------------------------------------------------------------------------------------|----------|

| FIGURA 2.2 - REPRESENTAÇÃO SIMPLES DE DIAGRAMA UNIFILAR.                              | 20       |

| FIGURA 2.3 DIAGRAMA UNIFILAR DE 14 BARRAS PARA BENCHMARK DO IEEE                      | 23       |

| FIGURA 2.4 - MATRIZ DE ADMITÂNCIA.                                                    | 25       |

| FIGURA 2.5 - FLUXOGRAMA DO NEWTON-RAPHSON PARA SOLUÇÃO DO FLUXO DE CARGA              | 29       |

| FIGURA 3.1 – ILUSTRAÇÃO DE CHAMADA A EXECUÇÃO DE INSTRUÇÃO EM GPU                     | 34       |

| FIGURA 3.2 – EXEMPLO DE INCONSISTÊNCIA DE WARP                                        | 35       |

| FIGURA 3.3 – MODELO DE PROJETO DAS ARQUITETURAS DA CPUS E GPUS                        | 36       |

| FIGURA 3.4 - MODELO DO HARDWARE E SUA HIERARQUIA DE MEMÓRIA                           | 37       |

| FIGURA 3.5 - ESCALABILIDADE DA PLATAFORMA CUDA                                        | 38       |

| FIGURA 3.6 - PARALELISMO DINÂMICO CUDA                                                | 40       |

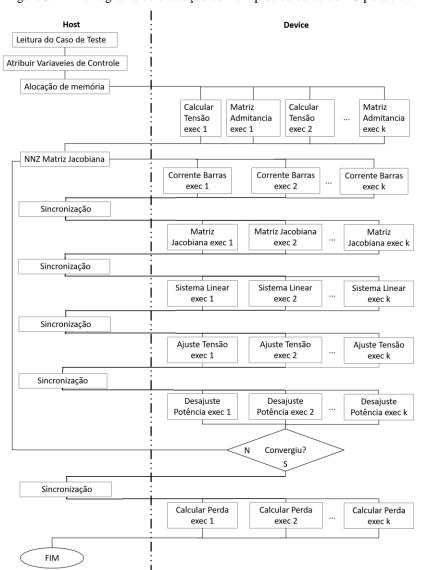

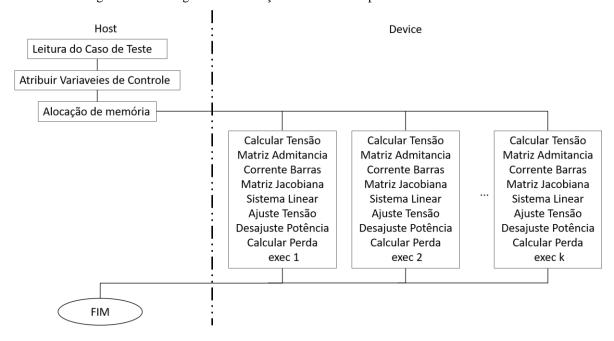

| FIGURA 5.1 – FLUXOGRAMA DE EXECUÇÃO DE MÚLTIPLOS CÁLCULOS DO FC PARALELO              | 53       |

| FIGURA 5.2 - FLUXOGRAMA DE EXECUÇÃO DA VERSÃO COM PARALELISMO DINÂMICO CUDA           | 59       |

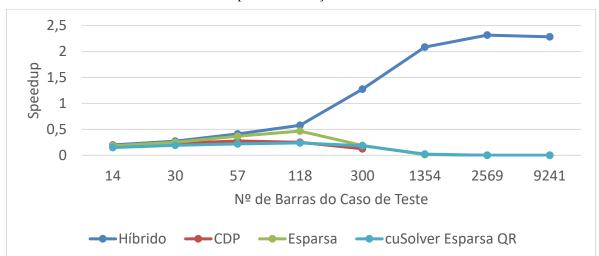

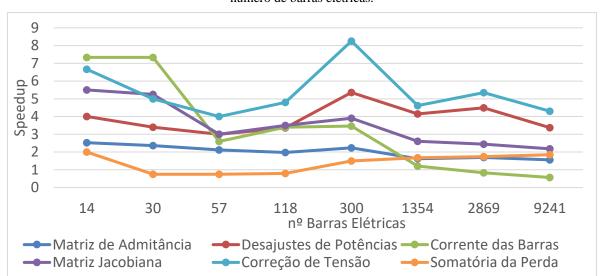

| FIGURA 6.1- SPEEDUP DAS 4 VERSÕES PARALELAS DO FLUXO DE CARGA VARIANDO O CASO DE      | <u> </u> |

| TESTE DE 14 ATÉ 9241 BARRAS ELÉTRICAS PARA 200 EXECUÇÕES SIMULTÂNEAS                  | 63       |

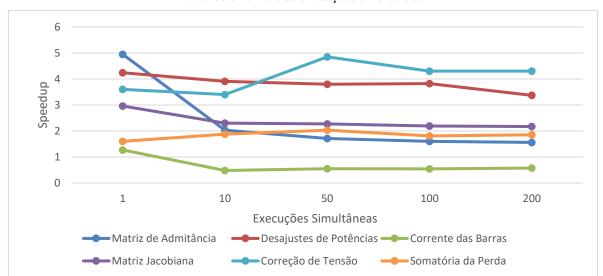

| FIGURA $6.2$ - SPEEDUP DAS ETAPAS DO FC EM GPU DA VERSÃO HÍBRIDA PARA O CASO DE TEST  | Е        |

| DE 9241 BARRAS VARIANDO O NÚMERO DE EXECUÇÕES SIMULTÂNEAS.                            | 65       |

| FIGURA $6.3$ - SPEEDUP DAS ETAPAS DO FC EM GPU DA VERSÃO HÍBRIDA PARA $200$ EXECUÇÕES |          |

| SIMULTÂNEAS VARIANDO O NÚMERO DE BARRAS ELÉTRICAS                                     | 66       |

## LISTA DE TABELAS

| TABELA 2.1 CLASSIFICAÇÃO DAS BARRAS ELÉTRICAS                                      | 21  |

|------------------------------------------------------------------------------------|-----|

| TABELA 4.1 – RESUMO DOS TRABALHOS CORRELATOS                                       | 46  |

| TABELA 5.1 - CASOS DE TESTES DE SISTEMAS ELÉTRICOS DE POTÊNCIA                     | 49  |

| TABELA 5.2 - PSEUDOCÓDIGO DA VERSÃO SEQUENCIAL                                     | 50  |

| TABELA 5.3 - TESTE COM EIGEN E MKL                                                 | 52  |

| TABELA 5.4 - PSEUDOCÓDIGO, COM SPEEDUP E OS TEMPOS EM SEGUNDOS DE CPU E GPU DE CA  | DA  |

| ETAPA DO FC PARA 200 EXECUÇÕES SIMULTÂNEAS COM O CASO DE TESTE DE 300 BARRAS       | \$  |

| ELÉTRICAS                                                                          | 55  |

| TABELA 5.5 - PSEUDOCÓDIGO, COM O SPEEDUP E OS TEMPOS EM SEGUNDOS DE CPU, GPU COM   |     |

| MATRIZES ESPARSAS E DENSAS DE CADA ETAPA DO FC PARA 200 EXECUÇÕES SIMULTÂNE        | EAS |

| COM O CASO DE TESTE DE 300 BARRAS ELÉTRICAS                                        | 56  |

| TABELA 5.6 - PSEUDOCÓDIGO, COM SPEEDUP E OS TEMPOS EM SEGUNDOS DE VERSÃO           |     |

| SEQUENCIAL E DA VERSÃO HIBRIDA PARALELIZADA DAS ETAPAS DO FC PARA 200              |     |

| EXECUÇÕES SIMULTÂNEAS COM O CASO DE TESTE DE 300 BARRAS ELÉTRICAS                  | 58  |

| TABELA 5.7 - TEMPO EM SEGUNDOS DA EXECUÇÃO TOTAL DA VERSÃO SEQUENCIAL, HIBRIDA I   | E   |

| COM CDP, JUNTAMENTE COM O <i>SPEEDUP</i> DA SEQUENCIAL PELO CDP, PARA 200 EXECUÇÕE | ES  |

| SIMULTÂNEAS COM O CASO DE TESTE DE 300 BARRAS ELÉTRICAS.                           | 60  |

| TABELA 5.8 – TEMPO(S) E SPEEDUP DE TODAS AS ESTRATÉGIAS PARA O CASO DE 300 BARRAS  |     |

| ELÉTRICAS COM 200 EXECUÇÕES SIMULTÂNEAS                                            | 61  |

| TABELA 6.1 - TEMPO(S) DAS 4 VERSÕES PARALELAS DO FLUXO DE CARGA E DA VERSÃO        |     |

| SEQUENCIAL, VARIANDO O CASO DE TESTE DE 14 ATÉ 9241 BARRAS ELÉTRICAS PARA 200      |     |

| EXECUÇÕES SIMULTÂNEAS                                                              | 63  |

| TABELA 6.2 - PSEUDOCÓDIGO COM OS TEMPOS EM SEGUNDOS DE TODAS AS VERSÕES DAS        |     |

| ETAPAS DO FC PARA 1 EXECUÇÃO COM O CASO DE TESTE DE 14 BARRAS ELÉTRICAS            | 64  |

| TABELA 6.3 - SPEEDUP DAS ETAPAS DO FC EM GPU DA VERSÃO HÍBRIDA PARA O CASO DE TEST | E   |

| DE 9241 BARRAS VARIANDO O NÚMERO DE EXECUÇÕES SIMULTÂNEAS                          | 65  |

| TABELA 6.4 - SPEEDUP DAS ETAPAS DO FC EM GPU DA VERSÃO HÍBRIDA PARA 200 EXECUÇÕES  |     |

| SIMULTÂNEAS VARIANDO O NÚMERO DE BARRAS ELÉTRICAS                                  | 66  |

#### LISTA DE ABREVIATURAS E SIGLAS

AVR Automatic Voltage Regulator

CDP CUDA Dynamic Parallelism

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

FACTS Flexible Alternating Current Transmission System

FC Fluxo de Carga

FDPF Fast Decoupled Power Flow

GS Gauss-Seidel

GPGPU General Purpose Graphics Processing Unit

GPU Graphics Processing Unit

IEEE Instituto de Engenheiros Eletricistas e Eletrônicos

MKL Math Kernel Library

MP Multiprocessador

NLTC No Load Tap Changer

NR Newton-Raphson

OLTC On Load Tap Changer

PEGASE Pan European Grid Advanced Simulation and State Estimation

SEP Sistema Elétrico de Potência

ShR Shunt Reactor

ULA Unidade Lógica e Aritmética

#### **RESUMO**

O cálculo do fluxo de carga provê informações fundamentais em um sistema elétrico de potência, informações necessárias para que sejam realizados estudos nos sistemas. No entanto, o fluxo de carga só pode ser realizado em estado de regime permanente. Caso o sistema sofra alguma alteração, seja por variação nas cargas ou modificações dos equipamentos de controle, este cálculo é necessário ser refeito. Por essa necessidade, de constantemente ter que realizar o controle no fluxo de carga, começou-se uma busca por otimizar o tempo necessário desta tarefa. Uma das soluções abordadas para isso foi a utilização de computação paralela, a qual começou a ser utilizada a General Purpose Graphics Processing Unit (GPGPU) como uma alternativa de melhor custo benefício para execuções em arquiteturas paralelas, que consiste na utilização de Graphic Processing Units (GPU) não somente para processamento gráfico, mas também para propósitos gerais. Diversos trabalhos têm tirado proveito da utilização de GPGPU nos cálculos do fluxo de carga, contudo, não há um consenso sobre qual estratégia utilizar para paralelizar neste tipo de hardware, ficando a cargo de cada autor o trabalho de desenvolver seu próprio método, dificultando a utilização da arquitetura para a implementação desses cálculos, tanto para fins acadêmicos, quanto para o mercado. Pela falta de um consenso e palas divergências encontradas nos trabalhos, esta dissertação visa analisar as etapas do fluxo de carga, identificando quais estão mais aptas a paralelização em GPGPU com o intuito de realizar múltiplos cálculos do fluxo de carga simultâneos e reduzir o tempo necessário para o processamento, difundindo uma estratégia eficiente para sistemas de larga escala no mercado e no meio acadêmico, facilitando a replicação para trabalhos futuros com utilização de metaheurísticas para otimização de sistemas elétricos de potência.

Palavras-chave: Sistemas Elétricos de Potência, Fluxo de Carga, GPGPU, CUDA

#### **ABSTRACT**

The load flow calculation provides fundamental information for an electric power system. However, the load flow can only be carried out in the steady state, in the event of a system suffering any change, by variation in the loads or modifications of the control equipment, this calculation is necessary to be redone. Because of this need, frequently have to perform the load flow, a research has begun to optimize the time needed for this task. A General-Purpose Graphic Processing Unit (GPGPU) as a cost-effective alternative to parallel architecture runs, which has a GPU not only for graphics purposes but also for general purposes. Several works were taken for the use of GPGPU in load flow calculations, there is no consensus on the content of the material, being in charge of each one of the work of its own method, making it difficult to use the architecture for an implementation of calculations, both for academic purposes and for the market. Due to the lack of consensus and differences found in the work, this dissertation aims to analyze the steps of the load flow, identifying which is more suitable to parallelize in GPGPU in order to perform simultaneous load flow calculations and reduces the time required for the processing, an efficient strategy for large scale systems in the market and not academic environment, facilitate the replication for future works using metaheuristics for optimization of power electrical systems.

Keywords: Electric Power System, Power Flow, GPGPU, CUDA

## 1 INTRODUÇÃO

#### 1.1 MOTIVAÇÃO E DESCRIÇÃO GERAL DO PROBLEMA

O primeiro Sistema Elétrico de Potência com distribuição de energia para consumidores finais surgiu a partir da *Pearl Street Station*, a primeira fonte geradora de energia a vapor, desenvolvida por Thomas Edison em *New York* no ano de 1882. A *Pearl Street Station* inicialmente tinha potência para energizar 3.000 lâmpadas para 59 consumidores, utilizava corrente direta e devido as dificuldades de transporte desse tipo de energia, a estação supria eletricidade apenas em um raio de 800m de distância.

Atualmente, a energia elétrica é um recurso importante que contribui na melhoria da qualidade de saúde, segurança e acesso a informação dos seres humanos. Segundo o departamento de energia dos Estados Unidos, no ano de 2014, foram consumidos 20.7 trilhões de Quilowatt-hora (kWh) no mundo. Esse crescimento na demanda de energia elétrica, tornou os Sistemas Elétricos de Potência cada vez mais complexos.

O Fluxo de Carga é um estudo responsável por fornecer os dados das tensões e potências do Sistema Elétrico de Potência com base nos valores de cargas consumidas. A partir das informações resultantes, podem ser realizados outros estudos e análises nos sistemas, como: planejamentos futuros para o acréscimo de equipamentos ou componentes; analises dos sistemas em caso de contingências no fornecimento de energia elétrica; otimização dos sistemas para redução da perda de potência ativa durante a transmissão.

O Fluxo de carga é realizado em regime permanente (quando não há variação no sistema) devido os cálculos se basearem no consumo de carga. A exemplo, considerando uma indústria que usa de equipamentos pesados com alto consumo de energia, o desligamento das máquinas por motivo de intervalo dos funcionários causa uma variação na carga consumida no Sistema Elétrico de Potência, sendo necessário recalcular o Fluxo de Carga com os valores de consumo atuais. Adicionalmente, durante a transmissão da energia elétrica há diversos equipamentos de controle de tensão e potência reativa (VQC) ajustados para a carga anterior, tornando-se necessário realizar diversos cálculos das tensões e potências com diferentes combinações de valores dos equipamentos de controle, de forma a otimizar o sistema.

Todo esse processamento fora demandado apenas por causa do intervalo dos funcionários de uma indústria. Porém, e se ao término do intervalo na indústria em questão, ou em outra pertencente ao mesmo Sistema Elétrico de Potência, ocorrerem problemas técnicos nos equipamentos e forçarem o desligamento? Neste caso, todas as vezes em que as cargas consumidas são alteradas é necessário refazer esse processamento, para que se diminua o desperdício de energia elétrica e, consequentemente, os custos monetários na sua geração.

## 1.2 PROBLEMÁTICAS E LIMITAÇÕES ATUAIS

Nas décadas de 1970 e 1980, iniciaram-se os desenvolvimentos de trabalhos de pesquisa com o objetivo de reduzir o tempo de processamento do fluxo carga, onde foram desenvolvidos métodos de solução do Fluxo de Carga menos custosos computacionalmente como o Desacoplado Rápido(STOTT; ALSAC, 1974) e com a abordagem da computação paralela (HOUSOS; OMAR WING, 1979; RAFIAN; STERLING; IRVING, 1985; WANG et al., 1989). Tais trabalhos, em sua maioria, criavam algoritmos paralelos, porém não os testavam em arquiteturas com múltiplas unidades logicas aritméticas.

Na década de 1990, a abordagem mais utilizada no *design* de métodos paralelos para o cálculo do Fluxo de Carga, era a paralelização das tarefas e estruturas contidas nos métodos sequenciais bem consolidados na área (HUANG; ABUR, 1990; LAU; TYLAVSKY; BOSE, 1991), como Gauss-Seidel (HUANG; ONGSAKUL, 1994), Newton-Raphson (AMANO; ZECEVIC; SILJAK, 1996; JUN QIANG WU; BOSE, 1995) e Desacoplado Rápido (ELKEIB; DING; MARATUKULAM, 1994), embora alguns métodos específicos para ambientes paralelos também tenham sido desenvolvidos (CHEN; BERRY, 1993; WANG; HADJSAID; SABONNADIÈRE, 1999).

Como resultado da busca por ambientes de baixo custo no início do século XXI, as *Graphic Processing Units* (GPU) começaram a ser utilizadas como alternativa de ambiente paralelo para propósitos gerais (GPGPU), dado seu desempenho em operações de ponto flutuante e o baixo custo de aquisição do hardware. Aliado a isso, a busca pela padronização da programação paralela motivou o desenvolvimento de modelos de programação específicos para GPU.

A plataforma *Computer Unified Device Architecture* (CUDA) (NVIDIA CORPORATION, 2016a) desenvolvida pela NVIDIA; surgiu como um novo modelo para a programação em GPU e é considerada uma das mais utilizadas. Tal plataforma passou a ser utilizada, também, na paralelização de métodos de Fluxo de Carga(LI; LI, 2014; MEI YANG et al., 2012), apresentando bom desempenho quando aplicada a Sistemas Elétricos de Potência de larga escala.

Entretanto, não há na presente literatura um padrão de paralelização do Fluxo de Carga na plataforma CUDA, o que dificulta a replicação e utilização de forma eficiente da GPU para este fim, apesar de todos os trabalhos apresentarem um benefício com a utilização do periférico de computação gráfica.

Devido à falta de padronização, cada autor fica encarregado de desenvolver sua própria metodologia, ocasionando ocorrência de algumas divergências entre os trabalhos, como por exemplo, a opção pelo uso de matrizes densas ou esparsas. Pela pouca conectividade em sua estrutura, o Sistema Elétrico de Potência tem uma característica representativa de esparsidade; porém, devido à arquitetura do *hardware* da placa de vídeo, a plataforma CUDA tem um maior aproveitamento com matrizes densas. Diante disso, qual abordagem deve ser utilizada para o Fluxo de Carga? E quais etapas deste devem ser paralelizadas? Todas ou apenas as que consomem maior processamento?

#### 1.3 OBJETIVOS GERAIS

Diante do exposto, este trabalho consiste em um estudo de estratégias de paralelização de execuções múltiplas dos cálculos de Fluxo de Carga em GPGPU, investigando qual abordagem de matrizes é melhor para ser utilizada, visando a realização de tal estudo com testes em sistemas reais (com milhares de barras elétricas), e também analisar quais etapas do Fluxo de Carga melhor se adequam a arquitetura paralela. Como objetivos específicos considera-se: realizar múltiplos cálculos de tensão e potência concorrentemente; obter uma reposta rápida do processamento exigido pelo Fluxo de Carga; testar estratégias em Sistemas Elétricos de Potência de larga escala; e disponibilizar os códigos para que sejam utilizados como base, facilitando, com isso, a replicação deste trabalho, tanto para comunidade acadêmica quanto para o mercado.

#### 1.4 OBJETIVOS ESPECÍFICOS

A realização de múltiplos cálculos dos Fluxos de Carga simultâneos desenvolvidos nesta dissertação, tem o intuito de servir como referência para trabalhos futuros que utilizarão algoritmos baseados em população para otimizar os Sistemas Elétricos de Potência, bem como obter um melhor desempenho usando mais recursos disponíveis pela GPU, ao realizar os cálculos concorrentemente, uma vez que dependendo do tamanho do sistema ou da placa de vídeo que realiza o processamento, uma execução do Fluxo de Carga não irá usufruir de todos os recursos disponíveis.

A resposta rápida do processamento exigido pelo Fluxo de Carga será obtida a partir da paralelização com GPGPU. Para isso, serão realizados testes com bibliotecas e diferentes estratégias, onde busca-se tirar o maior aproveitamento da GPU e também da CPU, quando a tarefa não se adaptar totalmente à plataforma paralela.

Vale ressaltar que, este trabalho tem o intuito de formular uma metodologia padrão para paralelização do Fluxo de Carga em GPU, visto que não existe uma definida disponível para tal finalidade. Além disso, os códigos serão disponibilizados no GITHUB – serviço de *Web Hosting* compartilhado para projetos que usam o controle de versionamento Git – para facilitar a usabilidade e replicação do trabalho no meio acadêmico e comercial.

Outro ponto importante é que as simulações serão realizadas com casos de testes (de domínio público) de Sistemas Elétricos de Potência de larga escala. Visto que há uma tendência no crescimento dos sistemas e também uma agregação de diferentes tipos de geração de energia como hidroelétrica, eólica, fotovoltaica e nuclear.

## 1.5 ESTRUTURA DA DISSERTAÇÃO

A presente dissertação está organizada como segue:

No Capítulo 2 são apresentados os principais conceitos de um sistema elétrico de potência, quais são seus principais componentes e como é realizado o controle da energia elétrica. Serão fornecidas informações necessárias para o estudo de caso desta dissertação, que são o cálculo de Fluxo de Carga e os componentes de controle que o influenciam.

No Capítulo 3 será apresentado um pouco sobre o contexto histórico do processamento em GPU para propósitos gerais, a plataforma CUDA com suas principais definições e a arquitetura de *hardware* das placas gráficas. Diante o exposto neste capítulo, será possível ter uma compreensão maior acerca da paralelização em GPU, o que contribuirá para o desenvolvimento das estratégias de paralelização do Fluxo de Carga para múltiplas execuções e melhorará a eficiência do processamento, reduzindo o tempo necessário.

No Capítulo 4, alguns trabalhos relacionados a pesquisa são discutidos e assim será possível obter referências das metodologias de paralelização utilizadas e analisar divergências entre os trabalhos. A partir disso, serão realizadas estratégias de paralelização e testes para solucionar as divergências encontradas.

No Capítulo 5 serão apresentadas estratégias de paralelização elaboradas nesta dissertação, bem como suas principais vantagens e desvantagens.

Em seguida, o Capítulo 6 descreve como foram realizados os testes e os resultados obtidos, qual estratégia foi mais eficiente e sua divulgação na plataforma de compartilhamento de códigos, para se difundir no meio acadêmico e industrial. Vale ressaltar que são realizados os testes com bases de larga escala, visto que há uma tendência no crescimento dos sistemas.

Por fim, no Capítulo 7, serão expostas as conclusões, dificuldades e trabalhos futuros.

## 2 SISTEMAS ELÉTRICOS DE POTÊNCIA

#### 2.1 CONSIDERAÇÕES INICIAIS

Neste capitulo serão apresentados os conceitos de um sistema elétrico de potência, quais são seus principais componentes e como é realizado o controle da energia elétrica. Também serão citados quais estudos são realizados nestes sistemas, entrando em detalhes no estudo do fluxo de carga, mostrando sua importância e como é realizado.

Adicionalmente, será apresentado o histórico que une os principais trabalhos na interseção de computação paralela e fluxo de carga. Sendo assim, esse capitulo irá fornece as informações necessária para o estudo de caso desta dissertação, ou seja, o cálculo de fluxo de carga e os componentes de controle que o influenciam.

#### 2.2 ESTRUTURA DE UM SISTEMA ELÉTRICO DE POTÊNCIA

Um Sistema Elétricos de Potência (SEP) é uma rede de componentes interconectados, projetados para converter energia não elétrica contínua para a forma elétrica e transporta-la em distancias potencialmente grandes. Um SEP pode ser dividido em 03 (três) subsistemas: Geração, Transmissão e Distribuição (KUNDUR; BALU; LAUBY, 1994).

A Geração é responsável pela produção e injeção de energia elétrica dentro dos SEPs. De fato, os geradores são dispositivos capazes de converter energia não elétrica na forma elétrica. Tipicamente, a energia é produzida num gerador sob a forma de torque mecânico em um eixo rotativo, como por exemplo, estações hidroelétricas e eólicas. Porém, podem ser produzidas de outras formas, como por exemplo, através de estações térmicas, nucleares e fotovoltaicas.

O subsistema de Transmissão, atende ao requisito de transportar a energia elétrica das estações geradoras para as áreas consumidoras. Este transporte é realizado através das linhas de transmissão, o qual é necessário que seja feita em alta tensão, entre de 110-230 kV, ou extra-alta tensão, acima de 230 kV, para que possa haver menos perda de energia pelo efeito Joule (IEEE INDUSTRY APPLICATIONS SOCIETY. POWER SYSTEMS ENGINEERING COMMITTEE., 1994).

Por fim, o ultimo subsistema, o de Distribuição é responsável pela redução da tensão e fornecer a energia para os consumidores finais. A tensão é reduzida para Media Tensão, valores entre 1 kV e 110kV, afim de atender os consumidores indústrias como também é reduzida para Baixa Tensão, valores inferiores a 1 kV, atendendo a generalidade de consumidores domésticos (IEEE INDUSTRY APPLICATIONS SOCIETY. POWER SYSTEMS ENGINEERING COMMITTEE., 1994). A Figura 2.1 exibe um SEP identificando cada subsistema.

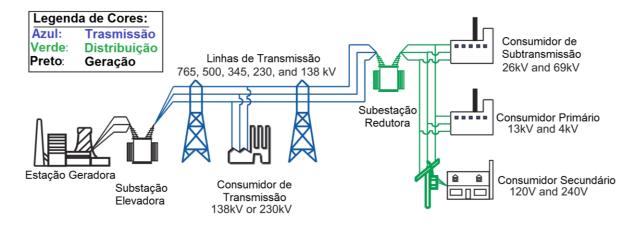

Figura 2.1 - Ilustração de um Sistema Elétrico de Potência. Fonte: Força Tarefa de Contingências de Sistemas Elétricos de Potência USA-Canadá.

A Figura 2.1 demonstra superficialmente o processo de geração, transmissão e distribuição da energia elétrica. Primeiramente, há uma estação geradora, o qual produzirá a energia elétrica, seguida de uma subestação elevadora, contendo os transformadores de energia para aumentar o valor de tensão. Enfim, essa energia é transportada pelas linhas de transmissão, que pode haver ou não consumidores nesta etapa, normalmente grandes fabrica e mineradoras. Ao chegar na área de consumo essa energia e passada novamente por uma subestação com transformadores, mas agora para reduzir o valor de tensão e fornecer a energia para as indústrias e residências.

A seguir será apresentado como um SEP é representado, a utilização de barras elétricas para conexão desses componentes, como são classificadas essas barras e quais

informações do SEP podem ser obtidas partir delas, para que assim possam ser realizados os estudos nestes sistemas.

#### 2.3 REPRESENTAÇÃO DE UM SISTEMA ELÉTRICO DE POTÊNCIA

A maioria da energia transmitida pelo mundo é realizada via sistema trifásico, sendo composto por 03 (três) ondas senoidais, defasadas em 120 graus entre si, de forma a equilibrar o sistema. Embora a estrutura de um SEP siga um sistema trifásico, para simplificação e entendimento o mesmo, via de regra é apresentado utilizando um sistema de diagrama unifilar, onde os elementos elétricos podem ser exibidos por símbolos esquemáticos padronizados e em vez de representar cada fase com uma linha separada, apenas 01 (um) condutor é representado. A partir desse diagrama, pode-se construir um circuito equivalente por fase para então prever o desempenho no sistema trifásico (GROSS, 1986).

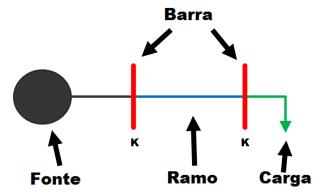

A Figura 2.2 demonstra um SEP simples representado por um diagrama unifilar. Percebe-se que existe uma fonte geradora de energia, uma linha de transmissão ou ramo e uma carga que representa um gasto de energia pelos consumidores. Também, pode-se notar, que entre estes componentes há barras elétricas realizando essa interconexão.

Figura 2.2 - Representação simples de Diagrama Unifilar.

As barras elétricas fornecem informação da energia em cada ponto de um SEP, podendo assim ser feita analises e estudos neste sistema. Cada barra k possui o valor de potência ativa  $P_k$ , potência reativa  $Q_k$ , magnitude da tensão nodal  $V_k$  e ângulo da tensão  $\theta_k$ ;

porém, dependendo das ligações existentes na barra, os valores de algumas variáveis serão conhecidos, enquanto outras terão que ser calculadas. A Tabela 2.1 apresenta os tipos de classificação das barras, de acordo com suas ligações, quais valores são conhecidos e quais são desconhecidos.

Variáveis Variáveis **Tipos** Características desconhecidas conhecidas PV Barras de geração  $P_k, V_k$  $Q_k, \theta_k$ PO Barras de carga  $P_k$ ,  $Q_k$  $V_k, \theta_k$  $V_k, \theta_k$ Barras de geração (geralmente uma Referência  $P_k, Q_k$  $(V\theta, slack, swing)$ unidade geradora de grande

capacidade)

Tabela 2.1 Classificação das barras elétricas.

As barras do tipo PV possuem as informações da potência ativa  $P_k$  e magnitude da tensão nodal  $V_k$ , isso por que estão conectadas a fontes geradoras de energia. Já a de referência também conhecida pelos termos V $\theta$ , Slack e Swing assim com PV, está ligada a uma fonte geradora, contudo em todo o SEP só há apenas 01 (uma) barra de referência, geralmente conectada a maior fonte geradora do sistema e por seu ângulo ser referência para as outras, são conhecidas a magnitude  $V_k$  e ângulo  $\theta_k$  da tensão nodal. Por fim as demais barras que não estão ligadas diretamente a componentes produtores de energia, as PQ são conhecidas a potência ativa  $P_k$  e reativa  $Q_k$  (BORGES, 2005).

Na próxima subseção serão apresentados alguns equipamentos de controle dos SEP presentes no subsistema de transmissão, estes são responsáveis por otimizar o sistema realizando ajustes na tensão e potência transportada. Também, para um melhor entendimento do SEP e seu relacionamento com os equipamentos, será introduzido um exemplo de estudo de caso *benchmark* de um diagrama unifilar de um caso de teste de SEP.

## 2.4 EQUIPAMENTOS DE CONTROLE EM SISTEMAS ELÉTRICOS DE POTÊNCIA

Modernos sistemas de transmissão têm aumentado o número de dispositivos eletrônicos de potência com o objetivo de aumentar o controle da transmissão de energia. O conjunto desses equipamentos de controle, para corrente alternada, é chamado de sistema de transmissão flexível em corrente alternada ou como conhecida em inglês por *Flexible Alternating Current Transmission System* (FACTS). Os equipamentos podem ser conjugados com soluções tradicionais, como compensações fixas em série ou shunt, de forma a complementar o sistema. A seguir será apresentado alguns desses dispositivos.

#### 2.4.1 Regulador Automático de Tensão

Os reguladores automáticos de tensão, conhecidos em inglês por *Automatic Voltage Regulator* (AVR), estão presentes em todos os geradores e compensadores síncronos do SEP. Estes dispositivos são compostos por diversos componentes como diodos, capacitores, resistores e potenciômetros até mesmo microcontroladores, tudo disposto em uma placa de circuito. Posicionados próximos dos geradores e conectados por um conjunto de fios para realizar as medições e ajuste do gerador. Os AVRs são utilizados para controlar a saída de energia da fonte geradora e manter constante o valor de tensão, porém um regulador não pode gerar energia, o valor de saída do equipamento sempre será menor ou igual ao de entrada.

#### 2.4.2 Transformador com *Tap* Variável

Os transformadores são usados para aumentar ou diminuir as tensões alternadas em SEPs, a partir da relação de espiras presente no enrolamento do transformador. Esses componentes que possuem o mecanismo de variação de *tap*, possibilitam a variação da relação de espiras, tendo vários pontos de acesso ao longo do enrolamento. Em transformadores com o *tap* variável existem dois tipos primários de variação do *tap*. Primeiro, que é necessário o transformador ser desenergizado, chamados de *No Load Tap Changer* (NLTC). Segundo, que pode ser ajustado durante a operação, chamado de *On Load Tap Changer* (OLTC). Com os OLTCs é possível realizar o ajuste da tensão transformada ao

longo do SEP, mantendo os valores de tensão próximos dos valores nominais e então manter a confiabilidade do SEP.

#### 2.4.3 Compensador Estático Fixo

No caso de linhas de transmissão muito longas, acima de 400 km, ocorre o Efeito Ferranti. Isto quer dizer, as linhas de transmissão têm um efeito capacitivo, que faz com que a tensão se eleve. Assim, sem uma compensação reativa, a tensão de regime no final da linha de transmissão é sempre maior do que no início. Os compensadores estáticos fixos, como por exemplo um reator shunt, *Shunt Reactor* (ShR), injetam uma potência reativa  $Q_k$  no SEP, já que  $Q_k$  é inversamente proporcional ao modulo da tensão  $V_k$ , ao aumentar  $Q_k$  diminui-se  $V_k$ .

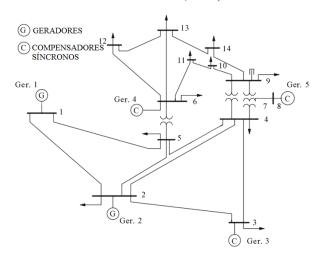

A Figura 2.3 é um diagrama unifilar representando um caso de teste para benchmark do Instituto de Engenheiros Eletricistas e Eletrônicos (IEEE) com 14 barras elétricas. Percebe-se a presença de geradores e compensadores síncronos nas barras de número 1, 2, 3, 4 e 8, sendo a barra 1 do tipo de referência, pois está ligada a fonte de maior geração do SEP e as demais sendo do tipo PV, pois estão ligadas a fontes geradoras. As barras onde não são injetadas tensão no SEP são do tipo PQ. Nota-se também a presença de transformadores entre as barras 5-6, 4-9 e um transformador com 03 (três) enrolamentos entre as barras 4,8 e 9. Por fim, pode-se verificar a presença de um compensador estático fixo na barra 9.

Figura 2.3 Diagrama Unifilar de 14 barras para benchmark do IEEE. Fonte: (UNIVERSITY OF WASHINGTON, 2017)

Na seção 2.3, vimos as diferentes classificações de barras elétricas, quais variáveis são conhecidas em cada tipo e quais são necessários ser calculadas, na próxima seção será apresento o cálculo do fluxo de carga, o qual pode-se obter os outros valores desconhecidos das barras elétricas.

#### 2.5 FLUXO DE CARGA

Fluxo de Carga (FC), chamado também de Fluxo de Potência é um estudo de SEP, realizado em estado estacionário do sistema, quando está operando em regime permanente, com o objetivo de determinar as características de operação estável dos sistemas de geração e transmissão de um SEP, dado um conjunto de barras elétricas de carga. A solução esperada são as informações, o ângulo e magnitude da tensão, assim como a potência ativa e reativa de cada unidade de transmissão, as perdas de potência durante a transmissão e a quantidade de energia reativa gerada/absorvida barra com tensão controlada.

O FC realiza uma modelagem do SEP, em forma de equações algébricas não lineares, mas antes de saber como é feita esta modelagem, é necessário ter uma maior compreensão sobre matrizes de admitância, o que será explicado na seção a seguir.

#### 2.5.1 Matriz de Admitância

A matriz de admitância Y, representa quando o valor de  $Y_{ij} \neq 0$ , que a barra i possui uma conexão direta com a barra j e vice-versa, seja por linha de transmissão ou por transformador. A admitância y é obtida pelo inverso da impedância Z exibido pela equação (2.1). A partir das informações de resistência r e reatância x das linhas de transmissão, temse o valor de impedância Z, logo, o valor de y. A equação (2.2), mostra a relação entre a corrente complexa  $I^*$  e tensão complexa E, onde E pode ser representado pela magnitude da tensão V e ângulo da tensão  $\theta$ . A Figura 2.4 demonstra a equação (2.2) em forma de matriz para um SEP com n barras elétricas.

$$y = Z^{-1} \mid Z = r + jx \tag{2.1}$$

$$I_k^* = \sum_{i=0}^n Y_{ki} * E_i | E_i = V_i \angle \theta_i$$

(2.2)

Figura 2.4 - Matriz de Admitância.

O cálculo de cada elemento da matriz de admitância é realizada conforme a equação (2.3), onde os elementos cuja os valores de i e j são diferentes, utiliza apenas o valor negativo da admitância entre a barra i e j, no outro caso, realiza-se uma somatória das admitâncias de todas as linhas de transmissão que terminam na barra i.

$$Y_{ij} = \begin{cases} i = j, & \sum_{k=0 \neq i}^{n} y_{ik} \\ i \neq j, & -y_{ij} \end{cases}$$

(2.3)

Visto como é feita o preenchimento da matriz de admitância e sua relação com a corrente e tensão, na próxima seção será apresenta a modelagem do SEP para equações algébricas e quais os principais métodos computacionais de resolução.

#### 2.5.2 Modelagem do Fluxo de Carga

Como dito no Capitulo 2.3, existem diferentes tipos de barra e o fluxo de carga irá fornecer as informações a priori desconhecidas dessas barras. A equação para o cálculo das potencias pode ser visto em (2.4) onde cada barra k possui uma potência  $S_k$  que pode ser decomposta em potência ativa  $P_k$  e reativa  $Q_k$  obtendo esse resultado pela multiplicação da tensão  $E_k$  e corrente  $I_k^*$ . Fazendo a substituição do  $I_k^*$  da equação (2.2) em (2.4),depois desenvolvendo o resultado e separando a parte real da imaginaria, adquire-se as equações

(2.5) e (2.6), onde a parte real é a potência ativa  $P_k$  e parte imaginaria é a potência reativa  $Q_k$  (GROSS, 1986).

$$S_k = P_k * jQ_k = E_k * I_k^* (2.4)$$

$$P_k = \sum_{m=0}^{n} V_k V_m \left( G_{km\cos\theta_{km} + B_{km}\sin\theta_{km}} \right)$$

(2.5)

$$Q_k = \sum_{m=0}^n V_k V_m \left( G_{km \sin \theta_{km} - B_{km} \cos \theta_{km}} \right)$$

(2.6)

Devido à variedade de tipos de barras essas equações (2.5) e (2.6) compõem 02 (dois) subsistemas.

#### 2.5.2.1 Subsistema 1

Este subsistema contém as equações que devem ser resolvidas para se encontrar o módulo e ângulo das tensões nas barras, para isso estipula-se os valores de  $V_k$  e  $\theta_k$  para as barras do tipo PQ e o valor de  $\theta_k$  para barras do tipo PV que se aproximem de seus conhecidos valores de  $P_k$  e  $Q_k$  de acordo com as equações deste subsistema.

$$\begin{cases} P_k = P_{k(V,\theta)}, & k \in \{PV, PQ\} \\ Q_k = Q_{k(V,\theta)}, & k \in \{PQ\} \end{cases}$$

(2.7)

#### 2.5.2.2 Subsistema 2

Este subsistema contém as equações que devem ser resolvidas para se encontrar a potência ativa e reativa nas barras, para isso utiliza-se os valores obtidos no Subsistema 1.

$$\begin{cases} P_k = P_{k(V,\theta)}, & k \in \{V\theta\} \\ Q_k = Q_{k(V,\theta)}, & k \in \{V\theta, PV\} \end{cases}$$

(2.8)

Essa aproximação realizada dos valores de potência a partir do modulo e ângulo da tensão do subsistema 1, pode ser feita de forma analítica, porém para casos de SEPs muito grandes, esta forma se torna impraticável, como também pode ser feita de forma computacional, para isto tem-se algumas técnicas como Gauss-Seidel, Newton-Raphson e Desacoplado rápido (BORGES, 2005).

O método de Gauss-Seidel (GS) é o mais antigo para a solução do fluxo de carga. É simples, confiável e geralmente tolerante a condições de baixas tensões e potência reativa. Apesar de ter um baixo consumo de memória, seu tempo de convergência tem crescimento rápido com relação ao aumento do tamanho do SEP. Este método possui uma lenta taxa de convergência e apresenta um problema de convergência para sistemas com altos níveis de potência ativa transferida.

O método de Newton-Raphson (NR) tem uma boa taxa de convergência. Seu tempo computacional tem um crescimento apenas linear ao tamanho do SEP. Este método, tem problemas de convergência para o caso de valores inicias serem estipulados muito diferentes dos valores reais, por isto não está apto a inicialização de tensão "*flat*", termo usado quando os valores inicias são atribuídos 1 (um) para módulo e 0 (zero) para o angulo da tensão. Além de ser necessário o cálculo da matriz jacobiana em cada iteração. O NR é adequado a sistemas de larga escala, o qual necessitam de soluções precisas.

O método Desacoplado Rápido, também conhecido em inglês por *Fast Decoupled Power Flow* (FDPF), é uma variação do método NR, não sendo necessário ser recalculado e refatorada a matriz jacobiana em cada iteração, assim diminui o tempo de processamento, porém aumento o número de iterações necessárias para obter a solução. Este método é menos sensível as condições de inicialização da tensão. Possui versões XB e BX, onde a primeira é negligenciado o efeito de resistência em série, por isso não é indicado para sistemas com altas taxas de resistência e reatância nas linhas de transmissão, sendo mais indicado para esses sistemas a segunda versão. O FDPF prover uma solução rápida e precisa para a maioria das condições de sistemas. Contudo, para sistemas como altos valores de ângulo de tensão pelas linhas de transmissão e com a presença de equipamentos de controle que influencia na potência ativa e reativa do SEP a utilização do NR pode ser necessária (KUNDUR; BALU; LAUBY, 1994).

Para este trabalho será utilizado o Método de NR, devido a sua adaptação a generalidade de condições de SEPs, tanto de sistemas pequenos e de grande escala, quanto a presença de equipamentos de controle, além de outros motivos que serão apresentados logo mais à frente no Capitulo 4, onde será exposto os trabalhos correlatos. A seguir será apresentado o método de NR para o problema de fluxo de carga.

#### 2.5.3 Solução do Fluxo de Carga pelo Método de Newton-Raphson

O método conforme mencionando na seção anterior, é um método mais genérico o qual aceita diversas condições do SEP. Um dos seus principais problemas está na inicialização dos valores de modulo e ângulo de tensão, para isso, usufrui-se de um seguinte princípio. Para o fluxo de carga, o sistema tem que estar em regime permanente, caso haja alguma alteração no SEP, seja nas cargas ou nos equipamentos de controle, o cálculo do FC tem que ser realizado novamente. Então, em vez de estipular os valores inicias completamente aleatórios ou pela inicialização de tensão "flat", e dado um direcional para esses valores, apropriando-se dos valores obtidos no cálculo do fluxo de carga anterior, os quais não vão esta corretos, mais estão mais próximos dos valores reais neste novo estado de regime permanente (KUNDUR; BALU; LAUBY, 1994).

Em um SEP novo, seja gerado do zero ou apenas realizando uma modificação em um sistema antigo, como por exemplo adicionar uma nova fonte geradora, neste caso não se tem os dados de um cálculo anterior, então é utilizado um outro método como GS ou FDPF para o 1º cálculo do FC e futuramente utilizar as informações anteriores no NR (KUNDUR; BALU; LAUBY, 1994).

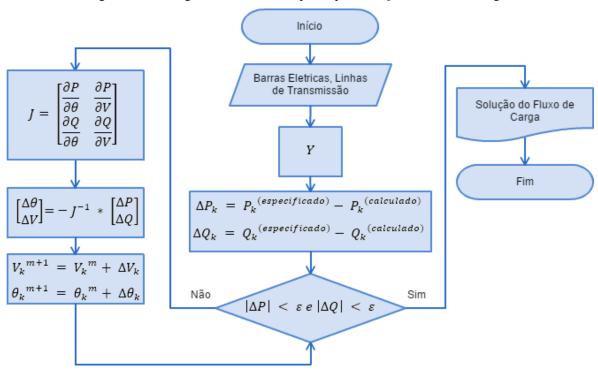

A Figura 2.5 exibe o fluxograma de execução do método NR. Primeiramente é realizada a leitura das informações de todas as barras elétricas e linhas de transmissão do SEP. Logo mais é realizado o cálculo da matriz de admitância, conforme mostrada na seção 2.5.1. Então, utilizando as equações (2.5) e (2.6) para o subsistema 1 apresentado na seção 2.5.2.1, calcula-se os valores de potência ativa  $P_k^{\ calculado}$  e reativa  $Q_k^{\ calculado}$  e comparados os valores dessas potências já conhecidas  $P_k^{\ especificado}$  e  $Q_k^{\ especificado}$ , obtendo assim os valores de desajustes das potências  $\Delta P_k$  e  $\Delta Q_k$ .

Com os valores de desajustes, verifica se o os critérios de parada foram satisfeitos, para isso, caso os valores máximo absoluto de desajuste da potência ativa  $|\Delta P|$  e reativa  $|\Delta Q|$  sejam menores que um valor de erro  $\varepsilon$  previamente definido, considera como o método convergido, inicia-se o processo de uma atualização dos valores de módulo e ângulo da tensão com base nesse desajuste das potências.

Figura 2.5 - Fluxograma do Newton-Raphson para Solução do Fluxo de Carga.

A matriz jacobiana é composta por quadrantes, onde em cada quadrante, tem-se uma derivada da potência em função de variável de modulo ou ângulo da tensão. Depois do cálculo da jacobiana, inverte-se a matriz para encontrar a variação de módulo  $\Delta V$  e ângulo  $\Delta \theta$  da tensão. A inversão pode ser realizada por uma resolução de sistemas lineares. Com as variações das variáveis da tensão, atualiza-se os valores com uma soma do valor atual mais a variação.

Com os novos valores de tensão, calcula-se novamente os desajustes de potência e verifica-se também o critério de parada, caso ainda não satisfeito, repete-se o processo até que se seja satisfeito. É comum também utilizar um outro critério de parada para não deixar executando muito tempo o método, que é o número máximo de iterações, os desajustes não satisfaçam o erro, mas quando o número de iterações máxima é atingida este método é

finalizado com os valores de tensão incorretos para o erro predefinido. Quando os critérios de parada são satisfeitos, o NR é finalizado com uma solução precisa das informações do SEP.

Como o FC provê somente as informações básicas de um SEP, e só pode ser realizado em estado estacionário, sendo necessário a realização do cálculo novamente quando houver qualquer alteração no sistema, buscou-se formas para que seu tempo de processamento fosse reduzido, para isso iniciaram estudos com o intuito de paralelizar os métodos de FC e então diminuir seu tempo. Na próxima seção será apresentado um breve histórico do paralelismo destes cálculos.

#### 2.6 PARALELISMO DO FLUXO DE CARGA

Com o surgimento da computação paralela como uma ferramenta de otimização, vislumbrou-se a oportunidade de aplicar esta abordagem no cálculo de FC, a fim de reduzir o custo em SEPs mais complexos. De acordo com (J. TYLAVSKY; BOSE, 1992), a motivação para a utilização de paralelismo neste problema está simplesmente no desejo de tornar a resolução do problema mais rápida, pois não há paralelismo inerente na estrutura matemática do FC, exceto para alguns dos métodos utilizados em sua solução. Neste âmbito, nas décadas de 1970 e 1980, iniciaram-se os desenvolvimentos de trabalhos com o intuito de se aproveitar da computação paralela para o cálculo do FC (HOUSOS; OMAR WING, 1979; RAFIAN; STERLING; IRVING, 1985; WANG et al., 1989). Tais trabalhos, em sua maioria, criavam algoritmos paralelos, porém não os testavam em arquiteturas paralelas, apenas teorizavam seus *speedups*, métrica de avalição de paralelização.

Na década de 1990, a abordagem mais comum no design de métodos paralelos para o cálculo do FC era a paralelização das tarefas e estruturas contidas nos métodos (sequenciais) bem consolidados na área (HUANG; ABUR, 1990; LAU; TYLAVSKY; BOSE, 1991) – como GS (HUANG; ONGSAKUL, 1994), NR (AMANO; ZECEVIC; SILJAK, 1996; JUN QIANG WU; BOSE, 1995) e FDLF (EL-KEIB; DING; MARATUKULAM, 1994), embora alguns métodos específicos para ambientes paralelos também tenham sido desenvolvidos (CHEN; BERRY, 1993; WANG; HADJSAID; SABONNADIÈRE, 1999). Esta abordagem facilita no designe e implementação paralela de

tais algoritmos, pois possibilita a reutilização de trabalhos e bibliotecas que já realizaram a paralelização das tarefas e estruturas necessárias para estes métodos.

Enquanto isso, esforços para fortalecer a área de computação paralela levaram a definições e padrões em 1992, no *Workshop on Standards for Message Passing in a Distributed Memory Environment* (BARNEY, 2016), com a direção para arquiteturas paralelas mais acessíveis para diversos problemas, inclusive no FC, como clusters de computadores, ao invés de supercomputadores (BALDICK et al., 1999; LI; BROADWATER, 2003).

Como resultado da busca por ambientes de baixo custo, no início do século XXI, as *Graphic Processing Units* (GPU) começaram a ser utilizadas como alternativa de ambiente paralelo, dada seu desempenho em operações de ponto flutuante e o baixo custo para adquirir o hardware. Aliado a isso, a busca por padronização da programação paralela motivou o desenvolvimento de modelos de programação paralela para GPU. Como um novo modelo para a programação em GPU, a plataforma *Computer Unified Device Architecture* (CUDA) (NVIDIA CORPORATION, 2016a) desenvolvida pela NVIDIA; ainda hoje em dia como uma das mais utilizadas em ambientes de computação em GPU. Tal plataforma passou a ser utilizada, também, na paralelização de métodos de FC (LI; LI, 2014; MEI YANG et al., 2012), apresentando bom desempenho quando aplicada a SEPs de larga escala.

## 2.7 CONSIDERAÇÕES FINAIS

Neste capitulo, vimos o que é um sistema elétrico de potência, quais seus componentes, equipamentos de controle e como representá-los. Também, foi apresentado o cálculo de fluxo de carga e seus diferentes métodos computacionais de solução, em mais detalhes, o método de Newton-Raphson, o que suporta a maioria de sistemas com diferentes condições. Adicionalmente, relatou-se um pequeno contexto histórico sobre o paralelismo do fluxo de carga, apontando diversos ambientes de computação paralela utilizadas e a mais recente, computação em GPU. No próximo capitulo, se mostra em mais detalhes a plataforma CUDA desenvolvida pela NVIDIA, para computação em placas de vídeo.

## 3 COMPUTAÇÃO PARALELA EM GPU

#### 3.1 CONSIDERAÇÕES INICIAIS

Neste capitulo será apresentado um pouco sobre o contexto histórico do processamento em GPU para propósitos gerais. Adicionalmente, será apresentado a plataforma CUDA que até o presente momento é uma das mais utilizadas nos trabalhos de paralização em GPU, por esta razão, será usada nesta dissertação. Complementarmente será exposto as principais definições, o fluxo de execução e arquitetura das placas gráficas com suporte a esta plataforma.

Diante no exposto neste capitulo, será possível ter uma compreensão maior da paralelização em GPU, o que contribuirá para o desenvolvimento das estratégias de paralelização na plataforma CUDA do Fluxo de Carga para múltiplas execuções e melhorar a eficiência do processamento, reduzindo o tempo necessário.

#### 3.2 CONTEXTO HISTÓRICO

No surgimento das placas de vídeo, seu principal objetivo era a realização de aceleração gráfica, permitindo apenas pipelines de função fixa específica. No final da década de 90, o hardware passou a ser mais programável, despertando o interesse não apenas de artistas e desenvolvedores de jogos, mas também, de pesquisadores, buscando aproveitar a desempenho de ponto flutuante desses periféricos. Assim, deu-se início ao termo de GPU de Propósitos Gerais (GPGPU – *General Purpose Graphics Processing Unit*). Entretanto, nesta época, a GPGPU não era simples de ser programável para propósitos gerais, pois, era necessário que os cálculos científicos fossem mapeados, e representados na forma de triângulos e polígonos.

Um grupo de pesquisadores da universidade de Stanford, liderados por Ian Buck, se reuniu para reformular a GPU como um *Streaming Processor*. Resultando em 2003, na anunciação da linguagem de programação Brook, um modelo de programação em linguagem de alto nível para GPGPU. Onde além de sua codificação ser bem mais simples, também era 7x mais rápido do que códigos similares existentes naquele período.

Em 2004 a NVIDIA, umas das principais empresas em computação gráfica, sabendo do potencial das placas gráficas, convidou Ian Buck a se juntar a sua equipe e começar a desenvolver uma solução para executar a linguagem de programação C na GPU de forma fluida, ocasionando em 2006 no anuncio da plataforma CUDA, a primeira solução do mundo para computação de propósito geral em GPUs e uma das mais utilizada até os dias de hoje em trabalhos de paralelismo com GPU (NVIDIA CORPORATION, 2016a).

A seguir será apresentado com mais detalhas a plataforma CUDA, as principais definições para o compreendimento do fluxo de execução e arquitetura das GPUs com suporte a CUDA.

#### 3.3 PLATAFORMA CUDA

A CUDA oferece suporte para linguagens de alto nível como Fortran, Java, Python, C#, MATLAB porém seu principal kit de desenvolvimento utiliza C/C++ como linguagem de programação. A plataforma vem sendo explorada por desenvolvedoras de grandes empresas como Adobe, ANSYS, Autodesk, MathWorks e Wolfram Research para executar computação científica de propósito geral e de engenharia em uma ampla variedade de softwares (NVIDIA CORPORATION, 2016a). A seguir será apresentado algumas definições utilizada pela plataforma.

#### 3.3.1 Principais definições

No desenvolvimento em CUDA, a CPU e a memória principal do computador são chamadas *host*, enquanto a GPU é chamada *device*, em um mesmo programa pode ser colocado instruções a serem executados por ambos. Entretanto, a execução deste programa começa no *host*, sendo necessário que se faça uma chamada para a execução no *device*. Esta chamada é feita por uma função especial, denominada *kernel*.

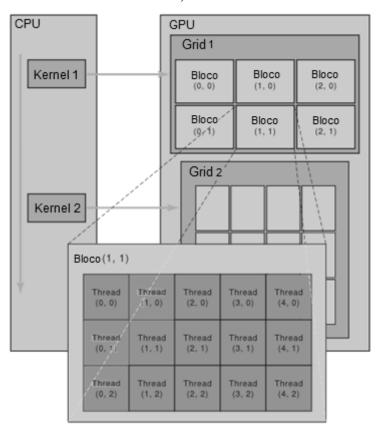

Quando é feita uma chamada para a execução de um *kernel*, constrói-se uma estrutura chamada *grid*. Esta estrutura é formada pelo conjunto de *threads* que executarão o código contido no *kernel* chamado. Estas, por sua vez, são separadas em blocos de *threads* com números iguais de *threads*. A Figura 3.1 demonstra o processo acima descrito de execução de instrução em GPU.

Figura 3.1 – Ilustração de chamada a execução de instrução em GPU. Fonte (NVIDIA CORPORATION, 2016b)

Percebe-se que na Figura 3.1 que é realizado dois *kernels* e cada um tem seu próprio *grid* de execução. No caso do primeiro *grid* são construídos 6 blocos de *thread*, onde cada um possui 15 *threads*, totalizando a execução de 90 *threads* para o primeiro *kernel*. Vale ressaltar que tanto o *grid* quanto o bloco de *threads* estão dispostos em duas dimensões, podendo ser em até três. Também é importante mencionar que a distribuição do número de *threads* por blocos, quantidades de blocos e suas dimensões, que totalizam o número de *threads* a ser executada pelo *kernel* é definida pelo desenvolvedor durante a chamada do *kernel*.

O modelo de execução em computação paralela pela taxonomia de Flynn (MONTEIRO, 2007) adotado na plataforma CUDA é *Single Instruction, Multiple Data* (SIMD), onde uma mesma instrução e realizada com múltiplos dados concorrentemente. No

caso das GPUs com suporte a essa plataforma são executadas 32 *threads* simultaneamente, esse conjunto é denominado *warp*.

O conhecimento de *warps* é importante para prevenir dois problemas que podem diminuir o desempenho, são esses: a ociosidade de *threads* e a inconsistência de *warps*. O primeiro, se refere a não utilização de um número de *threads* suficientes para completar um *warp*, isto quer dizer que terão threads do *warp* ociosas, indicando que não está sendo aproveitado o máximo que a GPU pode oferecer. O segundo, é quando existem instruções condicionais a ser executa em que uma condição é realizada por parte das *threads* de um *warp* e a outra condição pelas *threads* restantes. A Figura 3.2 demonstra um exemplo de inconsistência de *warp*.

Legenda Tempo Thread Thread Thread Thread (Clocks) 01 02 03 04 Thread Ativa Instrução 01 Se Condição 01 Entao Instrução 02 Senão Instrução 03 Instrução 04 Instrução 05 Instrução 06 Fim-se

Figura 3.2 – Exemplo de inconsistência de warp

A Figura 3.2 mostra apenas 4 *threads*, por meio de sua análise é possível perceber que por causa da *thread* 03 houve muita ociosidade das outras *threads*. Pelo fato de todas as *threads* de um *warp* executarem baseados em SIMD, essas threads terminaram o processamento no mesmo instante de tempo. Por esta razão, deve-se tentar manipular o desenvolvimento para que as condições sejam executadas em mesmo *warp* ao máximo.

Na próxima seção será apresentada a arquitetura das placas de vídeo com suporte a plataforma, mostrando as principais diferenças com a CPU e citando pontos onde pode ser obtido um melhor aproveitamento do *hardware*.

#### 3.3.2 Arquitetura do Hardware

A filosofia de *design* das GPUs, foi moldada pelo rápido crescimento das indústrias de jogos eletrônicos, que exerceram uma grande pressão econômica, pela capacidade de realizar massivos cálculos de números de ponto flutuante, por *frame* de vídeo nos jogos mais avançados. Esta demanda motivou as fabricantes de placas gráficas a aumentarem seus esforços para criar uma nova arquitetura do hardware, reduzindo o consumo de energia e maximizando a área dos chips para cálculos de pontos flutuantes, dessa forma otimizando a taxa de transferência em execução de grandes quantidades de *threads* (KIRK; HWU, 2013).

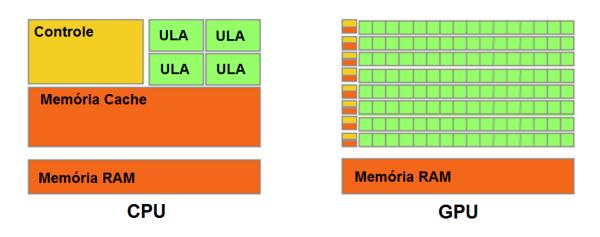

Por outro lado, as CPUs foram projetadas para diminuir a latência de uma única *thread*, com uma grande área do chip voltada para memória cache que armazena os dados mais frequentes afim de reduzir o tempo de acesso a essa informação. A Figura 3.3 ilustra uma representação das duas arquiteturas.

Figura 3.3 – Modelo de projeto das arquiteturas da CPUs e GPUs. Fonte: (NVIDIA CORPORATION, 2016b)

Pode-se observar na Figura 3.3 que a CPU possui uma sofisticada Unidade de Controle (UC) e de Unidades Logicas Aritméticas (ULAs), além de reservar boa parte de seu chip para memória cache. Enquanto a GPU diminui as ULA, tornando-as mais simples e reduz o tamanho da UC e memória cache, com a finalidade de aumentar o número de ULAs.

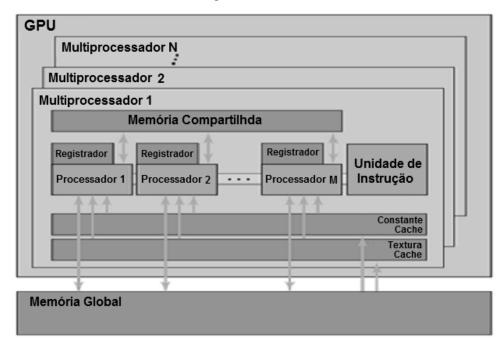

As GPUs com suporte a CUDA são compostas por um conjunto de N Multiprocessadores (MPs), onde cada MP possui um conjunto de M processadores chamados

de núcleos CUDA. A Figura 3.4 apresenta a arquitetura do hardware das GPU e sua organização quanto aos MPs e dos núcleos CUDA.

Figura 3.4 - Modelo do hardware e sua hierarquia de memória. Fonte: (NVIDIA CORPORATION, 2016b)

Na Figura 3.4 percebe-se a hierarquia de memória da placa gráfica constituída por 3 níveis: memória global, memória interna ao MP e memória interna ao núcleo CUDA. A memória global é acessível por todos os MPs; memórias internas ao MP que são manipuláveis por cada núcleo CUDA de um mesmo MP e são divididas em 2 tipos, a memória compartilhada e as memorias de cache (de variável constante e texturas) que armazenam cópias do que há na memória global. A memória interna ao núcleo CUDA são os registradores, controlado apenas por seus próprios núcleos.

As Memórias Globais são consideradas de longa latência, cerca de centenas de ciclos de *clocks* são necessários para seu acesso. Contudo, a transferência de dados da memória da CPU com a GPU só é realizada por este nível de memória. Em vista disso, uma boa gerencia da utilização dos níveis de memória é fundamental para um maior benefício da paralização neste hardware, já os outros níveis de memórias são de baixa latência por serem memórias internas. Sendo assim, uma boa prática para reduzir esse impacto da latência da memória

global é realizar uma cópia do dado em uma das memórias internas, caso for utilizar esse dado mais de uma vez (KIRK; HWU, 2013).

Esse modelo de hardware baseado em MP e núcleos CUDA, contribui para uma escalabilidade automática da plataforma, permitindo que uma aplicação desta plataforma seja executada em diferentes placas de vídeo. Na seção a seguir será explicado com mais detalhe a escalabilidade proporcionada pela plataforma.

#### 3.3.3 Escalabilidade da Plataforma

Os limites de *threads* por blocos e blocos por MP da placa de vídeo possibilita a otimização da aplicação para a determinada GPU, fazendo o balanceamento de número de *threads* por blocos e quantidade de blocos do *kernel*. Todavia essas configurações do *kernel* podem ser generalizadas afim de tornar a aplicação executável em qualquer outro dispositivo periférico gráfico. Isto é possível devido ao modelo de hardware e software adotados pela plataforma, número de MPs e núcleos CUDA, número de blocos e quantidade de *threads* por bloco. A Figura 3.5 exibe um exemplo dessa escalabilidade onde uma aplicação CUDA é executada por 2 GPU com diferentes propriedades.

Aplicação CUDA Bloco 0 Bloco 1 Bloco 2 Bloco3 Bloco 5 Bloco 6 Bloco 7 Bloco 4 GPU com 2 MPs GPU com 4 MPs MP 1 MP 2 MP 3 MP 0 MP 0 Bloco 0 Bloco 1 Bloco 0 Bloco 1 Bloco 2 Bloco 3 Bloco3 Bloco 2 Bloco 5 Bloco 6 Bloco 5 Bloco 7 Bloco 6

Figura 3.5 - Escalabilidade da plataforma CUDA. Fonte: (NVIDIA CORPORATION, 2016b)

A aplicação da Figura 3.5, o *kernel* foi configurado para a execução de 8 blocos e testada em duas placas gráficas com diferentes quantidades de MP, mas com o mesmo limite de 1 bloco por MP. Na primeira são necessários 4 ciclos de execução de blocos, já que são agrupados de forma a ocupar os 2 MP disponíveis. Enquanto na segunda, por ter uma maior quantidade de MP, o dobro da primeira, a quantidade de ciclos de execução de blocos e reduzida pela metade.

Quando um *kernel*, não é suficiente para ocupar todos os MPs da GPU, para ter benefício máximo da GPU, pode-se executar múltiplos *kernels* concorrentemente, mas só pode ser feito em placa gráficas com arquitetura a partir da geração Kepler. Além disso, essa geração proporciona também a utilização de paralelismo dinâmico CUDA, uma outra forma de tentar aproveitar ao máximo a GPU, reduzindo a troca de informação entre CPU e GPU. Na próxima seção será apresentado com mais detalhes o paralelismo dinâmico CUDA.

### 3.3.4 Paralelismo Dinâmico CUDA

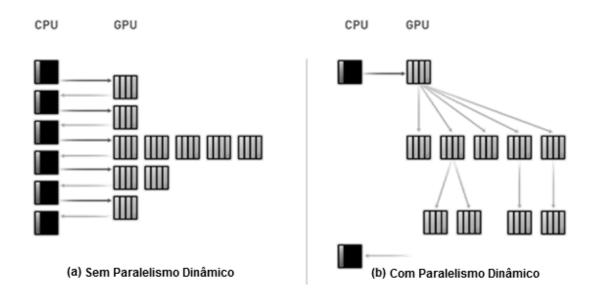

O paralelismo dinâmico em CUDA, *CUDA Dynamic Parallelism* (CDP), foi incluído a partir da arquitetura Kepler e é uma extensão ao modelo de programação CUDA, possibilitando a chamada de *kernels* a partir do *device* e não mais apenas do *host*, resultando em uma redução da necessidade de sincronismo com a CPU (NVIDIA CORPORATION, 2016b).

Com essa nova inclusão na plataforma, houve uma melhora da desempenho em algoritmos executados em GPU que utilizam recursão, estruturas irregulares de repetição, variação na memória consumida durante o tempo de execução. (WANG; YALAMANCHILI, 2014) realizaram um estudo sobre a utilização de CDP em GPU avaliando como métrica o potencial benefício de desempenho e no comportamento do fluxo de controle e de acesso a memória em um conjunto de aplicações de benchmark não estruturadas. Os testes mostraram que a utilização de CDP pode ser 1,13x-2,73x mais rápido do que sem a utilização, porém a sobrecarga do grande número de lançamentos de *kernels* pode negar esse benefício. A Figura 3.6 exibe a mudança de padrão de chamada de novos *kernels* com a inclusão do paralelismo dinâmico CUDA.

Figura 3.6 - Paralelismo Dinâmico CUDA. Fonte: (NVIDIA, 2012)

### Paralelismo Dinâmico

Percebe-se que na Figura 3.6(a) sem a presença do CDP, apenas a CPU pode realizar a chamada de *kernels*. Em contrapartida na Figura 3.6(b) a presença do CDP permite que *threads* em GPU façam a chamada de novos *kernels*. Além disso, é notório a diminuição da comunicação entre CPU e GPU.

# 3.4 MÉTRICAS DE AVALIAÇÃO

Em arquitetura de computador, o *speedup* é a métrica de desempenho entre dois sistemas que processam o mesmo trabalho, representando o ganho em velocidade de execução da determinada tarefa em duas arquiteturas similares com diferente arquitetura. O termo *speedup* foi definido por lei de Amdahl, a qual foca particularmente o processamento paralelo(HENNESSY; PATTERSON; ASANOVIĆ, 2012). Esta métrica pode ser obtida pela Equação

$$Speedup = \frac{T_s}{T_n} \tag{3.1}$$

Onde o  $T_s$  é o tempo de execução da versão sequencial e o  $T_n$  é o tempo de execução da versão paralelizada por n processos/processadores. O resultado varia entre 0 e n, tendo

um desempenho positivo para a versão paralela para valores acime de 1 (um). Caso o resultado seja inferior a 1 (um), o algoritmo paralelo é dito com menor eficiente do que sua versão sequencial, motivo pelo o qual dever ser analisado possíveis gargalos ou má utilização dos recursos disponíveis.

## 3.5 CONSIDERAÇÕES FINAIS

Neste capitulo, foi apresentado a plataforma CUDA, uma da mais utilizadas e bemconceituada plataforma para paralelismo em GPU, fato este que contribuiu para sua utilização nesta dissertação. Também, foram expostos alguns conhecimentos técnicos a respeito da arquitetura do hardware utilizado de forma a tirar vantagem ao máximo da placa gráfica. Por fim, foi mostrado um novo recurso disponíveis nas arquiteturas mais atuais, o paralelismo dinâmico CUDA, o que o torna ideal para múltiplas execuções simultâneas afim de usufruir de todos os MP da GPU e reduzir o sincronismo com a CPU.

O conhecimento a respeito da plataforma e da arquitetura do hardware, irão contribuir para o desenvolvimento das estratégias de paralelismo em GPU de múltiplos cálculos do Fluxo de Carga, mas ainda, é necessário obter informações de trabalhos acadêmicos similares, ou de interseção ao assunto de forma a refinar a base das estratégias que serão desenvolvidas. Tendo isso em vista, no próximo capitulo, serão apresentados os trabalhos correlatos do assunto deste trabalho.

### 4 TRABALHOS CORRELATOS

### 4.1 CONSIDERAÇÕES INICIAIS

Neste capítulo serão apresentados alguns trabalhos que fazem uso do Fluxo de Carga, também que realizam a paralelização, seja por cluster ou *multithread*, e aqueles que utilizaram apenas a plataforma CUDA para paralelizar o problema.

O conhecimento aprendido nesse capítulo contribuirá para o desenvolvimento das estratégias para múltiplas execuções simultâneas do Fluxo de Carga, como também colaborará para a aquisição de uma resposta rápida do processamento exigido. Na próxima seção serão apresentados alguns trabalhos que utilizam apenas o Fluxo de Carga sem a presença da computação paralela.

#### 4.2 FLUXO DE CARGA