Synchronization Algorithms for TDD Fronthaul in PTP-Unaware Networks

**Camila Novaes Silva**

**DM**: 08/23

UFPA / ITEC / PPGEE

Campus Universitário do Guamá

Belém-Pará-Brasil

2023

**Camila Novaes Silva**

Synchronization Algorithms for TDD Fronthaul in PTP-Unaware Networks

**DM**: 08/23

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil 2023

**Camila Novaes Silva**

#### Synchronization Algorithms for TDD Fronthaul in PTP-Unaware Networks

Submitted to the examination committee in the graduate department of Electrical Engineering at the Federal University of Pará in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering with emphasis in Telecommunications.

UFPA / ITEC / PPGEE Campus Universitário do Guamá Belém-Pará-Brasil 2023

Dados Internacionais de Catalogação na Publicação (CIP) de acordo com ISBD Sistema de Bibliotecas da Universidade Federal do Pará Gerada automaticamente pelo módulo Ficat, mediante os dados fornecidos pelo(a) autor(a)

S586s Silva, Camila Novaes. Synchronization algorithms for TDD fronthaul in PTPunaware networks / Camila Novaes Silva. — 2023. xxiv, 131 f. : il. color.

> Orientador(a): Prof. Dr. Aldebaro Barreto da Rocha Klautau Júnior

Dissertação (Mestrado) - Universidade Federal do Pará, Instituto de Tecnologia, Programa de Pós-Graduação em Engenharia Elétrica, Belém, 2023.

1. Sincronização de relógio. 2. PTP. 3. Arranjos de lógica programável em campo. 4. Ethernet. 5. Fronthaul. I. Título.

CDD 384

#### "SYNCHRONIZATION ALGORITHMS FOR TDD FRONTHAUL IN PTP-UNAWARE NETWORKS"

#### AUTORA: CAMILA NOVAES SILVA

DISSERTAÇÃO DE MESTRADO SUBMETIDA À BANCA EXAMINADORA APROVADA PELO COLEGIADO DO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA, SENDO JULGADA ADEQUADA PARA A OBTENÇÃO DO GRAU DE MESTRA EM ENGENHARIA ELÉTRICA NA ÁREA DE TELECOMUNICAÇÕES.

APROVADA EM: 17/03/2023

**BANCA EXAMINADORA:**

Prof. Dr. Aldebaro Barreto da Rocha Klautau Júnior (Orientador – PPGEE/UFPA)

Irenardo Lina Romalho

**Prof. Dr. Leonardo Lira Ramalho** (Avaliador Interno – PPGEE/UFPA)

Ednordo 1

**Prof. Dr. Eduardo Lins de Medeiros** (Avaliador Externo – ERICSSON)

**Prof. Dr. Igor Antônio Auad Freire** (Avaliador Externo – IFCOMM TELECOMUNICAÇÕES)

VISTO:

**Prof. Dr. Diego Lisboa Cardoso** (Coordenador do PPGEE/ITEC/UFPA)

## Acknowledgments

First, I would like to thank my advisor, Prof. Aldebaro Klautau, for all the guidance and support over the last six years. I am very grateful for his insights, knowledge, and motivational stories that allowed me to evolve not only professionally but also personally.

Secondly, I would like to thank the committee members, Dr. Eduardo Medeiros, Dr. Igor Freire, and Prof. Leonardo Ramalho. Their experience, insights, and comments were invaluable to the final version of this work.

Furthermore, I would like to extend my thanks to my colleagues at LASSE whom I enjoyed spending a terrific time in a very inspiring and friendly atmosphere. I would like to thank all the members that worked in the synchronization team over the years, particularly Igor Freire, Pedro Bemerguy, Rodrigo Dutra, and Juan Lopes, for their contributions to the testbed and software tools used in this work. Additionally, I would like to thank Igor Almeida for sharing his experience and thoughts on various aspects of this work.

I would like to thank the sponsors of this work, Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES), Brazil, and the Innovation Center, Ericsson Telecomunicações, Brazil.

Finally, I would like to especially thank my family, Lucivane, Junior, Fernanda, and Rafaela. Without their love and support, I would not have come this far.

Thank you all for your invaluable contributions to my academic journey.

Camila Novaes February 2023

# Glossary

| 4G    | Fourth-generation. 1, 3, 22                     |

|-------|-------------------------------------------------|

| 5G    | Fifth-generation. 1–3, 22                       |

|       |                                                 |

| ADC   | Analog To Digital Converter. 52                 |

| APTS  | Assisted Partial-timing Support. 4, 82, 92      |

| AVB   | Audio Video Bridging. 49                        |

| AxC   | Antenna Carrier. 50, 52–54, 60                  |

|       |                                                 |

| BBU   | Baseband Unit. 22, 23, 46–50, 52–55, 59, 60, 68 |

| BC    | Boundary Clock. 4, 14                           |

| BH    | Backhaul. 21, 22                                |

| BMC   | Best Master Clock. 13                           |

| BS    | Base Station. 1, 3, 21, 22                      |

|       |                                                 |

| C-RAN | Cloud Radio Access Network. 3, 21, 22           |

| CA    | Carrier Aggregation. 3                          |

| CBR   | Constant Bit Rate. 50, 52                       |

| CDAE  | Convolutional Denoising Autoencoder. 41         |

| CoMP  | Coordinated Multi-point. 3                      |

| CPRI  | Common Public Radio Interface. 3                |

| CRC   | Frame Check Sequence. 51                        |

| cTE   | Constant Time Error. 12                         |

|       |                                                 |

| DL    | Downlink. 22, 23, 51, 52, 54                    |

| DMA   | Direct Memory Access. 53                        |

| dTE          | Dynamic Time Error. 12                                                                                                                     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| FDD          | Frequency-division Duplex. 2                                                                                                               |

| FFM          | Flicker Frequency Modulation. 12                                                                                                           |

| FH           | Fronthaul. 3-6, 21-26, 28, 41-43, 45, 46, 50-53, 55,                                                                                       |

|              | 59-61, 65-68, 70, 73, 78-80, 92, 93                                                                                                        |

| FIFO         | First-in First-out. 52–54                                                                                                                  |

| FPGA         | Field-programmable Gate Array. 5, 46, 47, 50, 52                                                                                           |

| FPM          | Flicker Phase Modulation. 12                                                                                                               |

| FTS          | Full-timing Support. 4                                                                                                                     |

|              |                                                                                                                                            |

| GbE          | Gigabit Ethernet. 18, 46, 51, 59, 63                                                                                                       |

| GMII         | Gigabit Media-independent Interface. 50                                                                                                    |

| GNSS         | Global Navigation Satellite Systems. 1-4, 83                                                                                               |

|              |                                                                                                                                            |

| IoT          | Internet Of Things. 1                                                                                                                      |

| IQ           | In-phase And Quadrature. 50–55                                                                                                             |

|              |                                                                                                                                            |

| KF           | Kalman Filter. 6, 21, 33–38, 59, 80, 82–84, 87, 88, 91,                                                                                    |

|              | 92, 94, 95, 97, 99                                                                                                                         |

|              |                                                                                                                                            |

| LP           | Linear Programming. 33                                                                                                                     |

|              |                                                                                                                                            |

| LS           | Least Squares. 33                                                                                                                          |

| LS           | Least Squares. 33                                                                                                                          |

| LS<br>m-t-s  | Least Squares. 33<br>Master To Slave. 15, 17–19, 29, 31, 33, 38–43, 45, 55,                                                                |

|              | •                                                                                                                                          |

|              | Master To Slave. 15, 17–19, 29, 31, 33, 38–43, 45, 55,                                                                                     |

| m-t-s        | Master To Slave. 15, 17–19, 29, 31, 33, 38–43, 45, 55, 56, 61, 63, 64, 66–70, 72, 74–76, 78, 91                                            |

| m-t-s<br>MAC | Master To Slave. 15, 17–19, 29, 31, 33, 38–43, 45, 55, 56, 61, 63, 64, 66–70, 72, 74–76, 78, 91<br>Medium Access Control Layer. 17, 18, 51 |

MSE Mean-square Error. 82, 94, 99

| OC      | Ordinary Clocks. 14                                       |

|---------|-----------------------------------------------------------|

| OCXO    | Oven-controlled Crystal Oscillator. xvii, 48, 49, 60, 68, |

|         | 72, 74–76, 78–80, 83, 84, 87, 88, 90, 92                  |

|         |                                                           |

| PDV     | Packet Delay Variation. 2, 4, 5, 14, 15, 20, 21, 24, 32,  |

|         | 38–41, 65, 66, 91, 92                                     |

| PHY     | Physical Layer. 17–19, 41, 50, 62, 63, 82                 |

| ppb     | Parts Ber Bilion. 1                                       |

| PPS     | Pulse Per Second. 49                                      |

| PPS-RTC | PPS-synchronized RTC. 55, 56, 60                          |

| PRC     | Primary Reference Clock. 48                               |

| PRTC    | Primary Reference Time Clock. 14                          |

| РТР     | Precision Time Protocol. 2, 4–6, 13–15, 17–21, 23–26,     |

|         | 28-31, 33, 39-41, 45-50, 55-57, 59-68, 70, 72-74, 76,     |

|         | 78–80, 82, 83, 91–93                                      |

| PTP-DAL | PTP Dataset Analysis Library. 5, 47, 56–58, 61, 70, 72,   |

|         | 80, 82, 87, 88                                            |

| PTP-RTC | PTP-synchronized RTC. 55, 56, 60                          |

| PTS     | Partial-timing Support. 4, 21, 41                         |

|         |                                                           |

| QIA     | Queuing-induced Asymmetry. 42, 45, 59, 76, 78, 80, 82,    |

|         | 84, 87, 91, 92                                            |

|         |                                                           |

| RAN     | Radio Access Networks. 3, 21                              |

| RF      | Radio Frequency. 1, 3                                     |

| RRU     | Remote Radio Unit. 22, 23, 46–54, 59, 60, 68              |

| RTC     | Real-time Clock. 9, 31, 48, 49, 55                        |

| RWFM    | Random Walk Frequency Modulation. 12, 35                  |

| s-t-m | Slave To Master. 16-19, 29, 31, 33, 38-43, 45, 55, 56,              |

|-------|---------------------------------------------------------------------|

|       | 61, 63, 64, 67–70, 72, 74–76, 78, 91                                |

| SD    | Standard Deviation. 61, 62, 64                                      |

| SFD   | Start Of Frame Delimiter. 49, 51                                    |

| SFP   | Small Form-factor Pluggable. 47                                     |

| TAI   | International Atomic Time. 9                                        |

| TC    | Transparent Clock. 4, 14                                            |

|       | -                                                                   |

| TDD   | Time-division Duplex. 1, 3–5, 21–26, 28, 38, 39, 41, 42,            |

|       | 45, 49, 51–54, 59, 65, 66, 68, 70, 72, 74, 80, 91–93                |

| TDM   | Time-division Multiplexing. 3                                       |

| TE    | Time Error. 12                                                      |

| ToD   | Time Of Day. 9, 14                                                  |

| Tx    | Transmission. 52, 53                                                |

| UE    | User Equipment. 21, 23                                              |

| UL    | Uplink. 22, 23, 51, 52, 54, 68                                      |

| UTC   | Coordinated Universal Time. 9                                       |

| VLAN  | Virtual Local Area Network. xix, 47, 59, 61, 64, 65                 |

| WFM   | White Frequency Modulation. 12, 35                                  |

| WPM   | White Phase Modulation. 12                                          |

| XO    | Crystal Oscillator. xvii, 48, 60, 68, 72, 74, 76–80, 84, 87, 90, 92 |

# **Symbols**

| Α                    | State transition matrix. 35, 94, 96, 97                   |

|----------------------|-----------------------------------------------------------|

| $R_{line}$           | Ethernet bit rate. 18, 51                                 |

| $t_{21}^{\prime}[n]$ | Drift-compensated master-to-slave timestamp differ-       |

|                      | ences. 29, 30, 39                                         |

| $t_{43}^{\prime}[n]$ | Drift-compensated slave-to-master timestamp differ-       |

|                      | ences. 29, 31, 39                                         |

| D                    | Linear fractional frequency drift. 11, 12                 |

| $\gamma[n]$          | Noise associated with the delay asymmetry. 16, 19, 20,    |

|                      | 42                                                        |

| $\gamma_r[n]$        | Random components from delay asymmetry. 20                |

| $\gamma_s[n]$        | Static components from delay asymmetry. 20                |

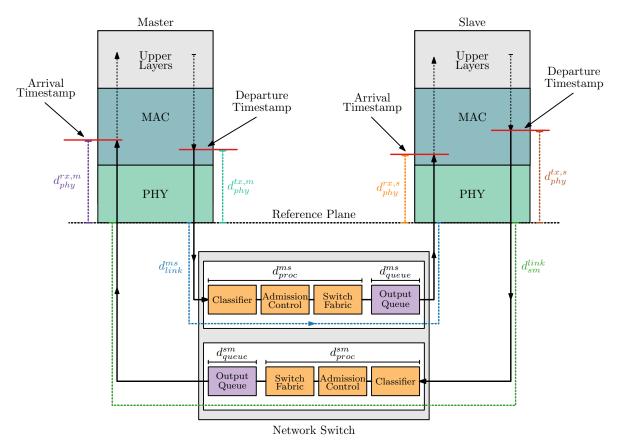

| $d_{link}[n]$        | Link level delay. 19                                      |

| $d_{link}^{ms}[n]$   | Link level delay in the master-to-slave direction. 18, 19 |

| $d^{sm}_{link}[n]$   | Link level delay in the slave-to-master direction. 18, 19 |

| $\gamma^m_{phy}[n]$  | Physical delay asymmetry from master node. 19             |

| $\gamma^s_{phy}[n]$  | Physical delay asymmetry from slave node. 19, 20          |

| $d_{phy}^{rx,m}[n]$  | Physical layer receive latency from master node. 18, 19   |

| $d_{phy}^{tx,m}[n]$  | Physical layer transmission delay from master node. 18,   |

|                      | 19                                                        |

| $d_{phy}^{rx,s}[n]$  | Physical layer receive latency from slave node. 18, 19    |

| $d_{phy}^{tx,s}[n]$  | Physical layer transmission delay from slave node. 18,    |

|                      | 19                                                        |

| $d_{proc}[n]$        | Processing delay. 19                                      |

|                      |                                                           |

$\gamma_{proc}[n]$  Switch Processing delay asymmetry. 19

- $d_{proc}^{ms}[n]$  Switch processing delay in the master-to-slave direction. 19

- $d_{proc}^{sm}[n]$  Switch processing delay in the slave-to-master direction. 19

- $d_{prop}[n]$  Propagation delay. 19

- $\gamma_{prop}[n]$  Propagation delay asymmetry. 19, 20

- $d_{prop}^{ms}[n]$  Propagation delay in the master-to-slave direction. 19

- $d_{prop}^{sm}[n]$  Propagation delay in the slave-to-master direction. 19

- $d_{queue}[n]$  Queuing delay. 19

- $\gamma_{queue}[n]$  Queueing delay asymmetry. 19

- $d_{queue}^{ms}[n]$  Switch queuing delay in the master-to-slave direction. 19

- $d_{queue}^{sm}[n]$  Switch queuing delay in the slave-to-master direction. 19

- $d_{trans}[n]$  Transmission delay. 18, 19

- $\gamma_{trans}[n]$  Transmission delay asymmetry. 19

- $d_{trans}^{ms}[n]$  Transmission delay in the master-to-slave direction. 19

- $d_{trans}^{sm}[n]$  Transmission delay in the slave-to-master direction. 19

- $\Delta d_{ms}[n]$  First difference of delays in master-to-slave direction. 42, 43

- $\Delta d_{sm}[n]$  First difference of delays in slave-to-master direction. 43

- $\Delta t_{21}[n]$  First difference of delays in master-to-slave direction. 43

- $\Delta t_{43}[n]$  First difference of delays in slave-to-master direction. 43

- $d_{ms}[n]$  True master-to-slave PTP delay. 15, 16, 19, 42, 55, 56

- $\hat{d}_{ms}[n]$  Estimated master-to-slave PTP delay. 15

- $d_{sm}[n]$  True slave-to-master PTP delay. 16, 19, 42, 55, 56

- f(t) Instantaneous frequency. 10, 11

- $f_{nom}$  Nominal frequency. 9–11

- $f_s$  Sampling frequency. 54

- h Observation transition vector. 36

- H Observation transition matrix. 94, 95, 98, 99

- $i_{fh}$  Period of FH packet. 50, 51

- I Identity matrix. 99

- $l_{iq}$  IQ samples size. 51, 60

| Κ                                                                                                                 | Kalman gain. 97–99                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\kappa_{ms}$                                                                                                     | Total static delay in master-to-slave direction. 42, 43                                                                                                                                                                                                                                                                                                                                                        |

| $\kappa_{sm}$                                                                                                     | Total static delay in slave-to-master direction. 42, 43                                                                                                                                                                                                                                                                                                                                                        |

| $\eta_a$                                                                                                          | Number of antenna streams. 50, 60                                                                                                                                                                                                                                                                                                                                                                              |

| $N_{bits}$                                                                                                        | Number of bits. 18                                                                                                                                                                                                                                                                                                                                                                                             |

| $\eta_{oh}$                                                                                                       | Ethernet overhead length. 51                                                                                                                                                                                                                                                                                                                                                                                   |

| $\eta_{spf}$                                                                                                      | Number of IQ samples per frame. 50, 51, 60                                                                                                                                                                                                                                                                                                                                                                     |

| u                                                                                                                 | Innovation vector. 97, 98                                                                                                                                                                                                                                                                                                                                                                                      |

| $\phi(t)$                                                                                                         | Random phase deviation. 10–12                                                                                                                                                                                                                                                                                                                                                                                  |

| Р                                                                                                                 | State estimation error covariance matrix. 37, 38, 96, 97,                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                   | 99                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\psi[n]$                                                                                                         | Time offset random noise. 35                                                                                                                                                                                                                                                                                                                                                                                   |

| $q_{ms}[n]$                                                                                                       | Total queuing delay in master-to-slave direction. 42, 43,                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                             |

| $q_{sm}[n]$                                                                                                       | Total queuing delay in slave-to-master direction. 42, 43,                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\mathbf{Q}$                                                                                                      | State noise covariance matrix. 36, 88, 90, 95, 97                                                                                                                                                                                                                                                                                                                                                              |

| r                                                                                                                 | Measurements noise covariance vector. 36                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                   | Measurement noise covariance matrix. 95, 99                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathbf{R}$                                                                                                      | Wedstrement noise covariance matrix. 55, 55                                                                                                                                                                                                                                                                                                                                                                    |

| ${f R}$ s                                                                                                         | State vector. 35–37, 94, 96, 97, 99                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                |

| S                                                                                                                 | State vector. 35–37, 94, 96, 97, 99                                                                                                                                                                                                                                                                                                                                                                            |

| s<br>ŝ                                                                                                            | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98                                                                                                                                                                                                                                                                                                                                           |

| ${f s}$<br>${f \hat s}$<br>$\Delta_x[n]$                                                                          | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98<br>Time offset drift. 29, 40                                                                                                                                                                                                                                                                                                              |

| ${f s}$<br>$\hat{f s}$<br>$\hat{\Delta}_x[n]$<br>$\hat{\Delta}_x[n]$                                              | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98<br>Time offset drift. 29, 40<br>Time offset drift estimate. 29                                                                                                                                                                                                                                                                            |

| f s<br>$\hat s$<br>$\Delta_x[n]$<br>$\hat \Delta_x[n]$<br>$t_{fh}$                                                | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98<br>Time offset drift. 29, 40<br>Time offset drift estimate. 29<br>FH packet transmission delay. 51, 60, 67                                                                                                                                                                                                                                |

| ${f s}$<br>${\hat s}$<br>${\hat \Delta}_x[n]$<br>${\hat \Delta}_x[n]$<br>$t_{fh}$<br>$t_{ipg}$                    | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98<br>Time offset drift. 29, 40<br>Time offset drift estimate. 29<br>FH packet transmission delay. 51, 60, 67<br>Ethernet's inter-packet gap. 51, 60, 67                                                                                                                                                                                     |

| ${f s}$<br>${\hat s}$<br>${\hat \Delta}_x[n]$<br>${\hat \Delta}_x[n]$<br>$t_{fh}$<br>$t_{ipg}$<br>$t_{ptp}$       | State vector. 35–37, 94, 96, 97, 99<br>Estimated State vector. 96–98<br>Time offset drift. 29, 40<br>Time offset drift estimate. 29<br>FH packet transmission delay. 51, 60, 67<br>Ethernet's inter-packet gap. 51, 60, 67<br>PTP packet transmission delay. 60, 67                                                                                                                                            |

| f s<br>$\hat s$<br>$\Delta_x[n]$<br>$\hat \Delta_x[n]$<br>$t_{fh}$<br>$t_{ipg}$<br>$t_{ptp}$<br>$T_s$             | <ul> <li>State vector. 35–37, 94, 96, 97, 99</li> <li>Estimated State vector. 96–98</li> <li>Time offset drift. 29, 40</li> <li>Time offset drift estimate. 29</li> <li>FH packet transmission delay. 51, 60, 67</li> <li>Ethernet's inter-packet gap. 51, 60, 67</li> <li>PTP packet transmission delay. 60, 67</li> <li>Sampling period. 50</li> </ul>                                                       |

| f s<br>$\hat s$<br>$\Delta_x[n]$<br>$\hat \Delta_x[n]$<br>$t_{fh}$<br>$t_{ipg}$<br>$t_{ptp}$<br>$T_s$<br>$t_1[n]$ | <ul> <li>State vector. 35–37, 94, 96, 97, 99</li> <li>Estimated State vector. 96–98</li> <li>Time offset drift. 29, 40</li> <li>Time offset drift estimate. 29</li> <li>FH packet transmission delay. 51, 60, 67</li> <li>Ethernet's inter-packet gap. 51, 60, 67</li> <li>PTP packet transmission delay. 60, 67</li> <li>Sampling period. 50</li> <li>Sync departure timestamp. 15, 16, 47, 55, 56</li> </ul> |

- $t_2^{pps}[n]$  Sync arrival timestamp according to the slave's PPS RTC.. 55, 56

- $t_3[n]$  DelayReq departure timestamp. 15, 16, 47, 55, 56

- $t_3^{pps}[n]$  DelayReq departure timestamp according to the slave's PPS RTC. 55, 56

- $t_4[n]$  DelayResp arrival timestamp. 15, 16, 47, 55, 56

- $t_{43}[n]$  Slave-to-master timestamp difference. 16, 29, 43, 45

- T(t) Clock time function. 11

- $\Phi(t)$  Total instantaneous phase. 10, 11

- $\hat{d}[n]$  Two-way delay measurement. 16

- V(t) Quasi-sinusoidal voltage. 10

- *v* Measurement noise vector. 94, 95

- v[n] Time offset measurement noise. 36

- $V_0$  Voltage amplitude. 10

- $\sigma_v^2$  Time offset measurements noise variance. 37

- $t'_{21}[k]$  k-th vector of drift-compensated master-to-slave timestamp differences. 39

- $t'_{43}[k]$  k-th vector of drift-compensated slave-to-master timestamp differences. 39

- $d_{ms}[k]$  k-th vector of master-to-slave delays. 38

- $d_{sm}[k]$  k-th vector of slave-to-master delays. 38

- $t_{21}[k]$  k-th vector of master-to-slave timestamp differences. 38

- $t_{43}[k]$  k-th vector of slave-to-master timestamp differences. 38

- w State noise vector. 35, 36, 94–97

- $\omega(t)$  Instantaneous angular frequency. 10

- $w_x[n]$  Time offset state noise. 35, 36

- $w_y[n]$  Frequency offset state noise. 35, 36

- x[n] Discrete-time time offset. 15, 16, 29, 35, 55, 56

- x(t) Continuous-time time offset. 11, 12

- $\hat{x}[n]$  Estimated discrete-time time offset. 38–40

- $\tilde{x}[n]$  Noisy discrete-time time offset. 15, 16

- $x_0$  Initial time offset. 11, 12

- y[n] Discrete-time frequency offset. 35

- y(t) Continuous-time frequency offset. 11, 12

- $\hat{y}[n]$  Estimated discrete-time frequency offset. 40

- $\tilde{y}[n]$  Noisy Discrete-time frequency offset. 16

- $y_0$  Initial frequency offset. 11, 12

- z Measurement vector. 94, 95, 97, 98

- z[n] Time offset measurements. 36

# **List of Figures**

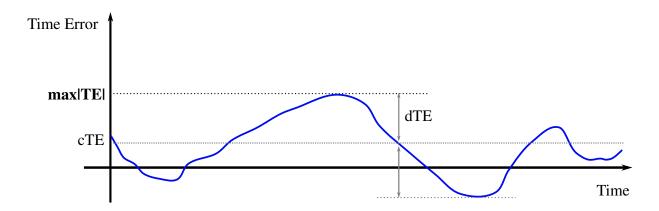

| 2.1  | Frequency, phase, and time synchronization.                                     | 8  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Measurements of time error between two clocks based on [1]                      | 12 |

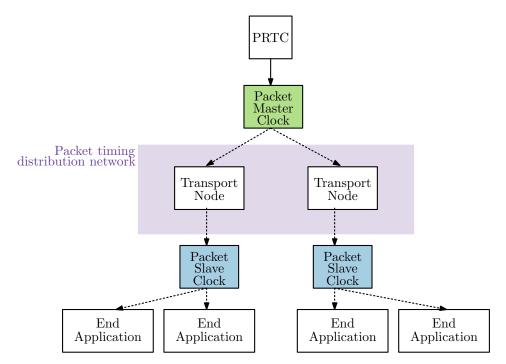

| 2.3  | PTP hierarchical architecture                                                   | 13 |

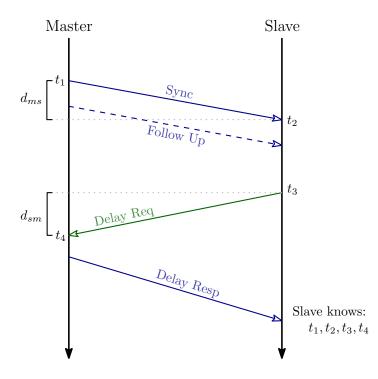

| 2.4  | PTP delay request-response mechanism.                                           | 14 |

| 2.5  | Illustration of packet delays between the timestamp point at the master and the |    |

|      | timestamp point at the slave node.                                              | 17 |

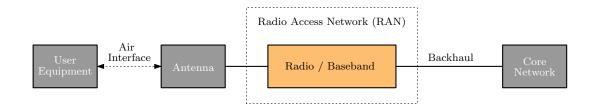

| 3.1  | Traditional mobile architecture                                                 | 22 |

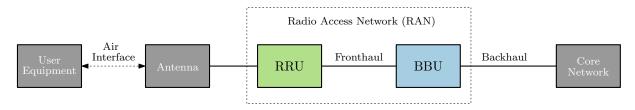

| 3.2  | C-RAN architecture.                                                             | 22 |

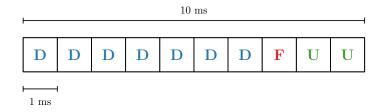

| 3.3  | Representation of TDD frame DDDDDDDDUU                                          | 23 |

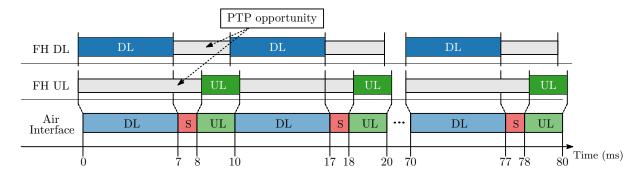

| 3.4  | Timing diagram for PTP transmit opportunity in FH (based on [2])                | 24 |

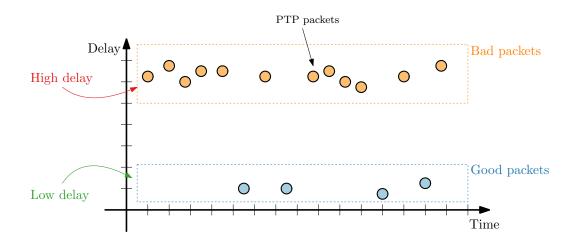

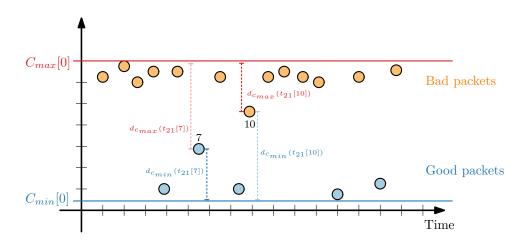

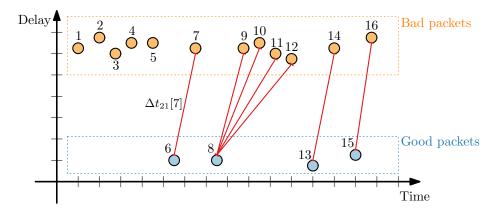

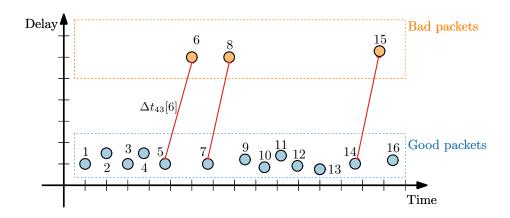

| 3.5  | Classification of PTP packets based on the experienced delays                   | 25 |

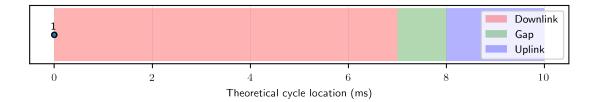

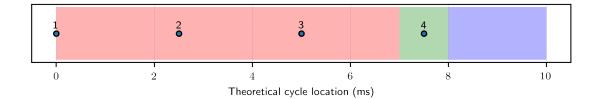

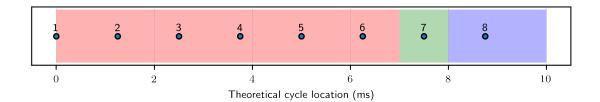

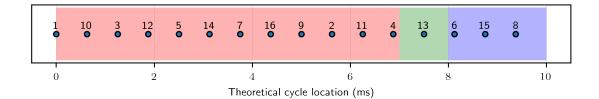

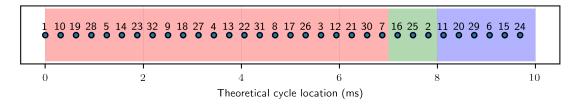

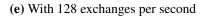

| 3.6  | PTP cycle location with different exchange periods and TDD frame with 7 ms      |    |

|      | of downlink, 1 ms of gap and 2 ms of uplink                                     | 27 |

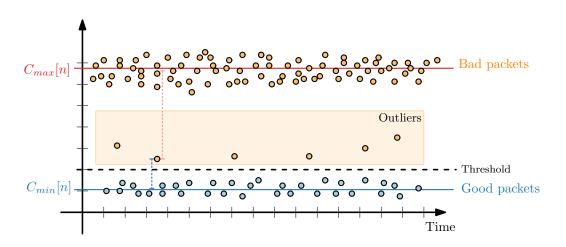

| 3.7  | Illustration of K-means classification process.                                 | 30 |

| 3.8  | Illustration of the K-means outlier threshold                                   | 31 |

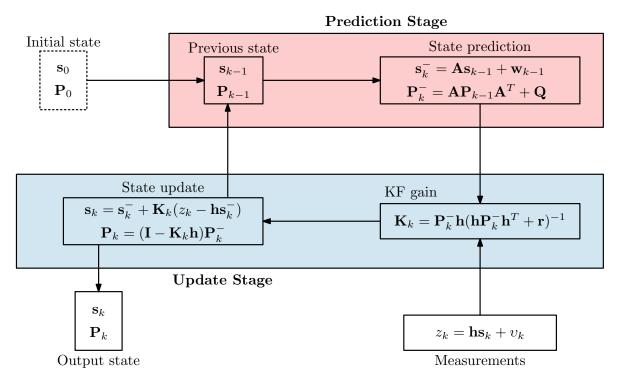

| 3.9  | Kalman filter loop.                                                             | 37 |

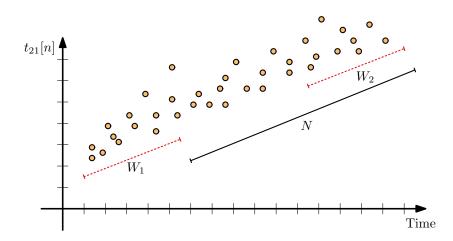

| 3.10 | Window-based filtering for time offset drift estimate.                          | 40 |

| 3.11 | Timestamp differences in the downlink direction.                                | 44 |

| 3.12 | Timestamp differences in the uplink direction.                                  | 44 |

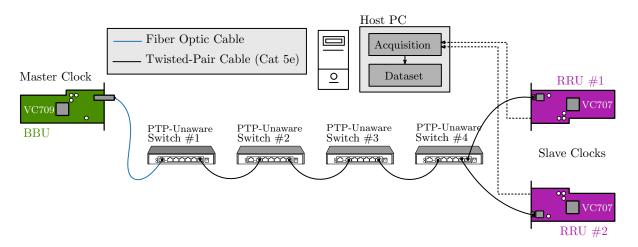

| 4.1  | Testbed overview.                                                               | 47 |

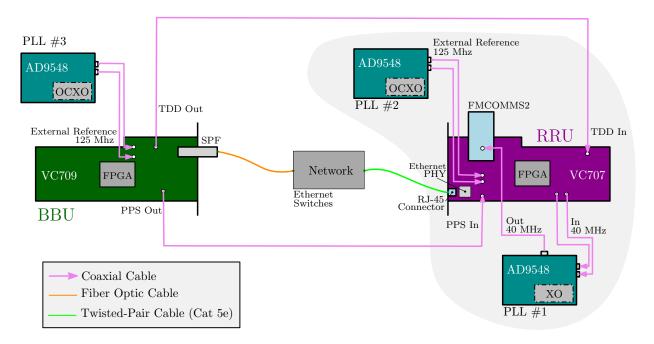

| 4.2  | Overview of the testbed connections and clock distribution paths                | 48 |

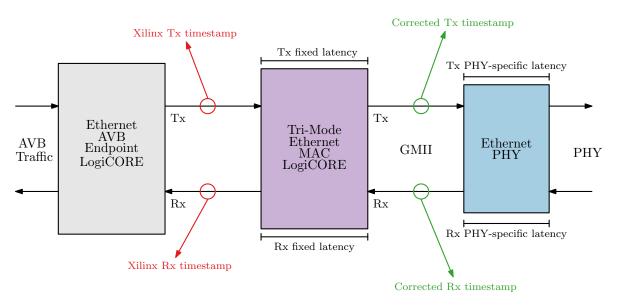

| 4.3  | Testbed timestamp position.                                                     | 49 |

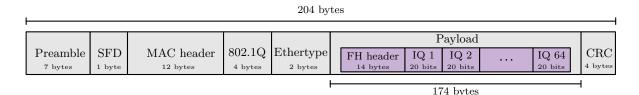

| 4.4  | Illustration of the FH packet structure                                         | 51 |

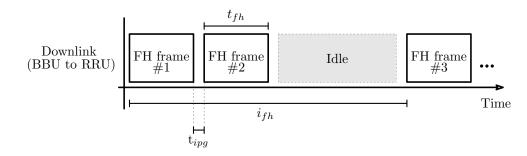

| 4.5  | Testbed traffic pattern in CBR FH                                               | 51 |

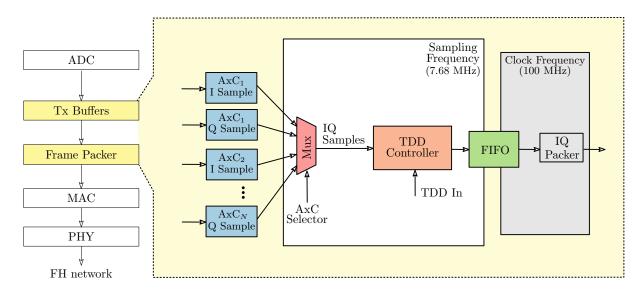

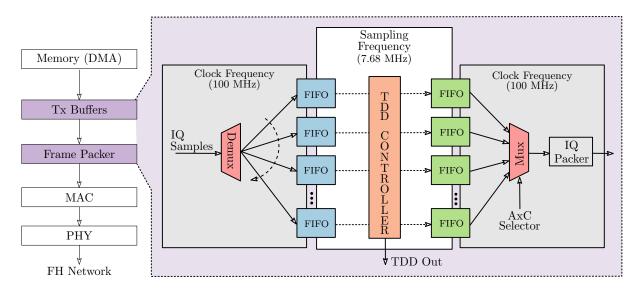

| 4.6  | Tx design for controlling the FH traffic at the RRU.                            | 52 |

|------|---------------------------------------------------------------------------------|----|

| 4.7  | Tx design for controlling the FH traffic at the BBU                             | 53 |

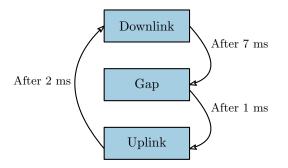

| 4.8  | TDD State machine                                                               | 54 |

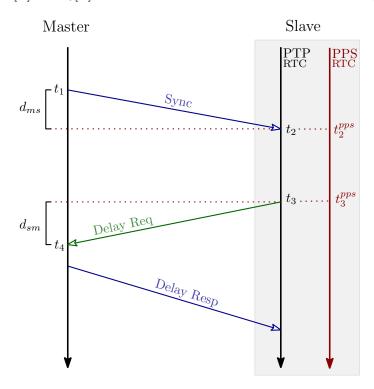

| 4.9  | PTP delay request-response mechanism.                                           | 56 |

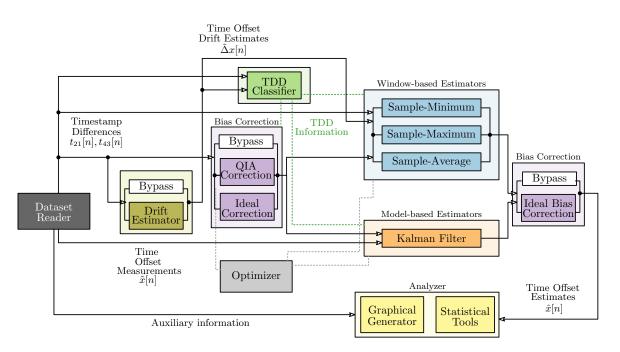

| 4.10 | PTP-DAL architecture.                                                           | 57 |

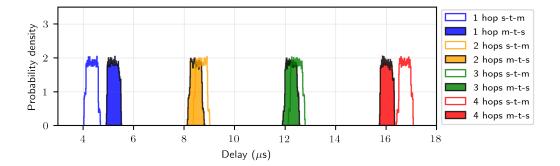

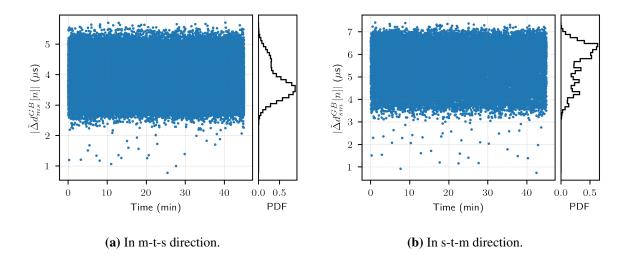

| 5.1  | True delay distribution in the m-t-s and s-t-m direction using port-based VLAN  |    |

| 5.1  | in a one to four-hop configuration in absence of FH traffic.                    | 62 |

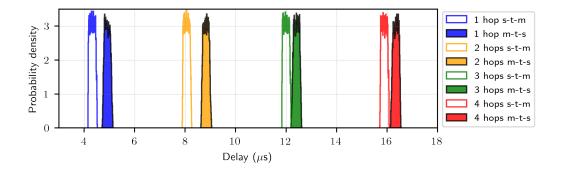

| 5.2  | True delay distribution in m-t-s and s-t-m direction using multiples physical   | 02 |

| 5.2  | switches in absence of FH traffic. The 1-hop configuration uses switch #4, 2-   |    |

|      | hops uses switches #4 and #1, 3-hops uses #4, #1 and #2 and 4-hops with all     |    |

|      | switches.                                                                       | 63 |

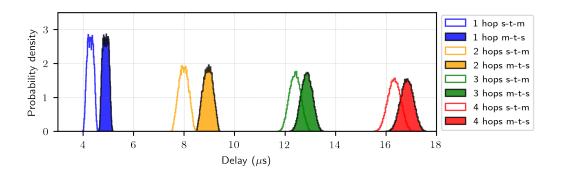

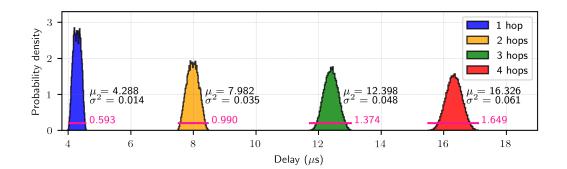

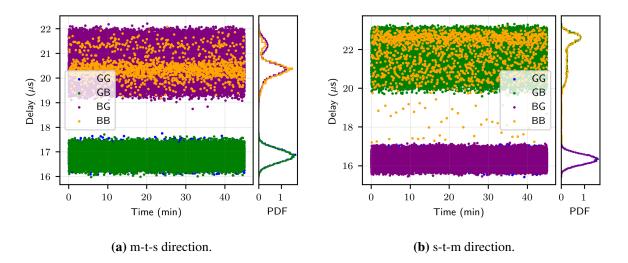

| 5.3  | Delay statistics in m-t-s direction using multiple physical switches.           | 65 |

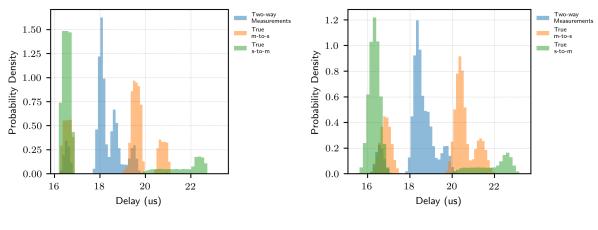

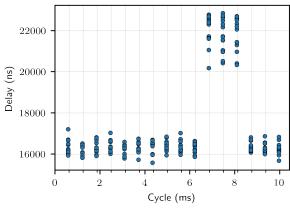

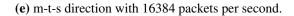

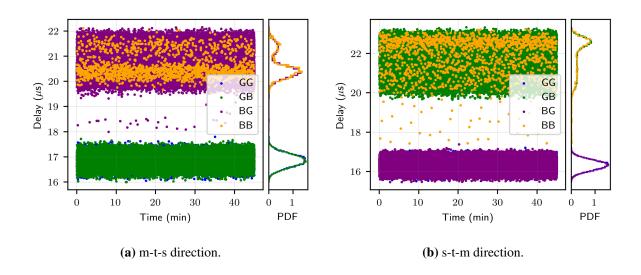

| 5.4  | Delay distribution with FH traffic.                                             | 66 |

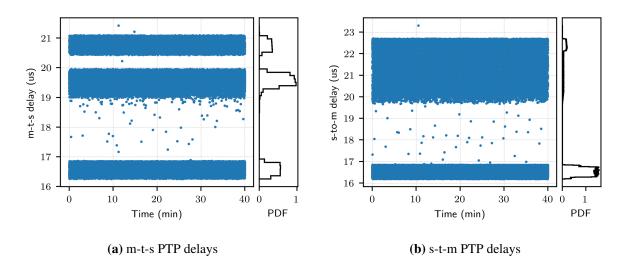

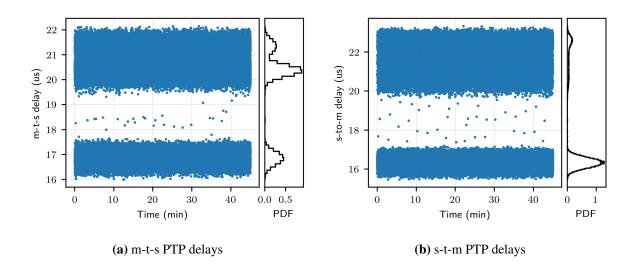

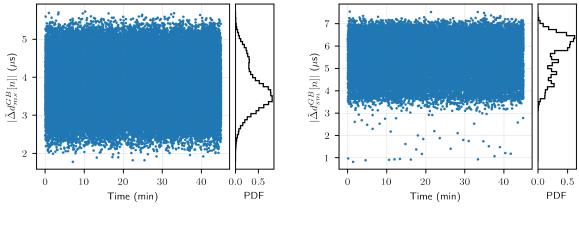

| 5.5  | Delay distribution and PDF using VLAN-based hops.                               | 67 |

| 5.6  | Delay distribution with FH traffic.                                             | 68 |

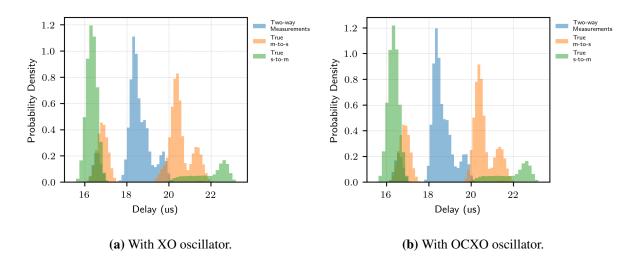

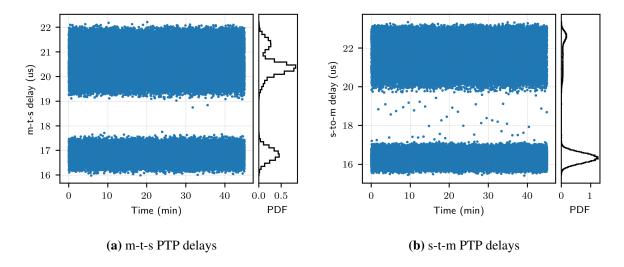

| 5.7  | Delay distribution and PDF using XO oscillator.                                 | 69 |

| 5.8  | Delay distribution and PDF using OCXO oscillator.                               | 69 |

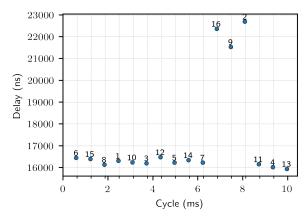

| 5.9  | PTP cycle location in the experiment with the XO oscillator.                    | 71 |

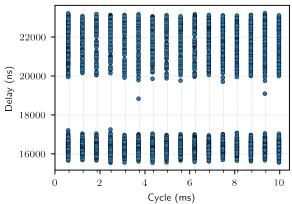

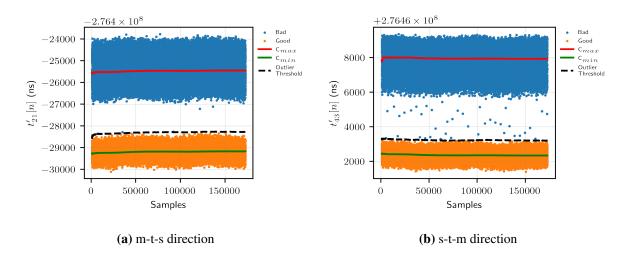

| 5.10 | K-means classification in the experiment with XO.                               | 73 |

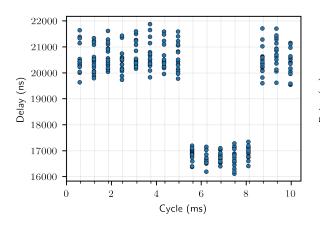

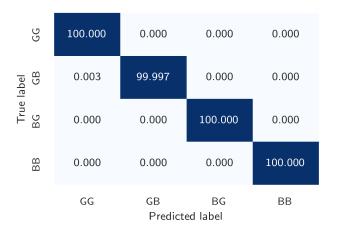

| 5.11 | Confusion matrix in the experiment with XO.                                     | 73 |

| 5.12 | TDD packet classification in the experiment with crystal oscillator (XO)        | 74 |

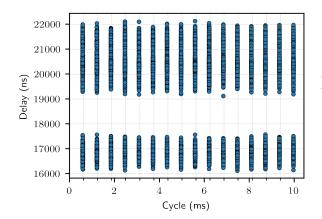

| 5.13 | TDD packet classification in the experiment with oven-controlled crystal oscil- |    |

|      | lator (OCXO)                                                                    | 75 |

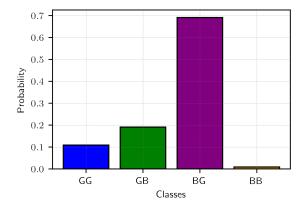

| 5.14 | Bar plot with the probability of each class calculated with the output from the |    |

|      | K-means classifier.                                                             | 75 |

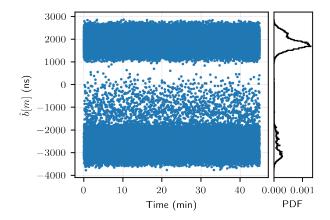

| 5.15 | Estimated delay difference in the experiment with XO oscillator.                | 76 |

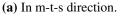

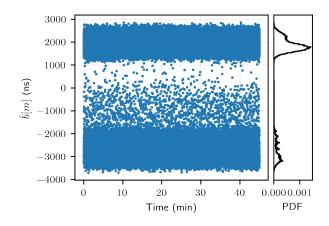

| 5.16 | Estimated QIA delay in the experiment with XO.                                  | 77 |

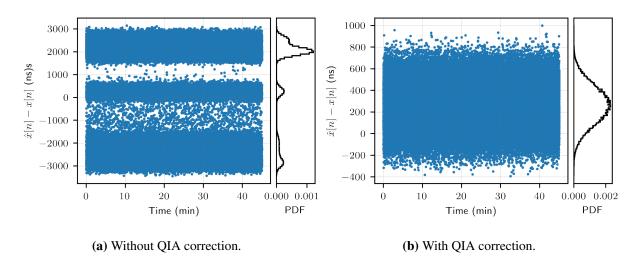

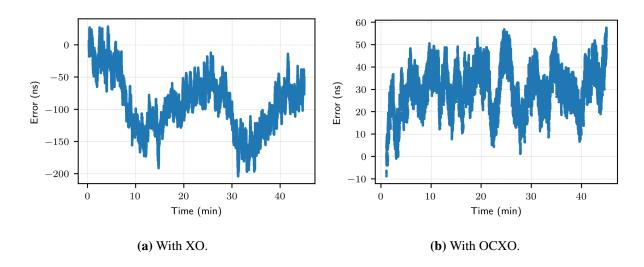

| 5.17 | Time offset measurements error in the experiment with XO                        | 77 |

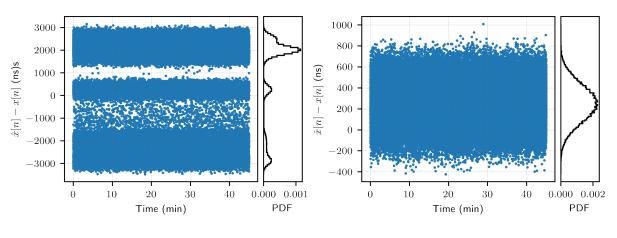

| 5.18 | Estimated delay difference in the experiment with OCXO oscillator               | 78 |

| 5.19 | Estimated QIA in the experiment with OCXO oscillator.                           | 78 |

| 5.20 | Time offset measurement error in the experiment with OCXO oscillator            | 79 |

|      |                                                                                 |    |

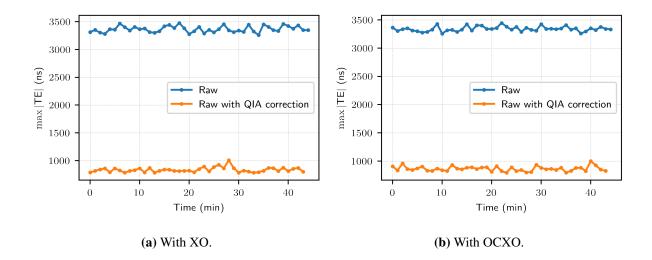

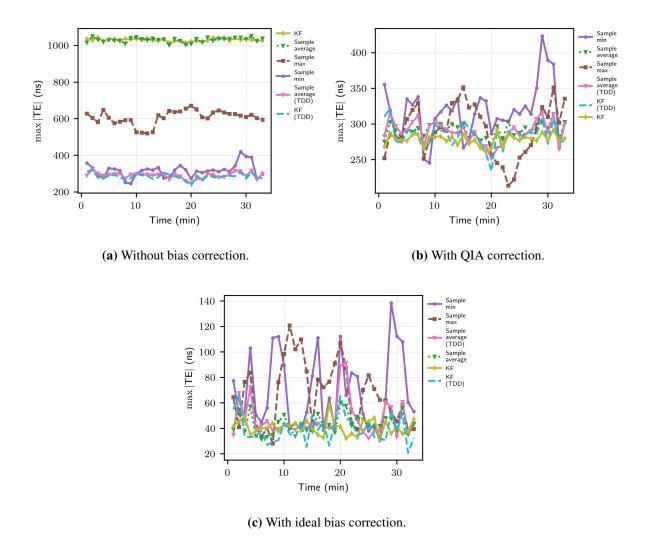

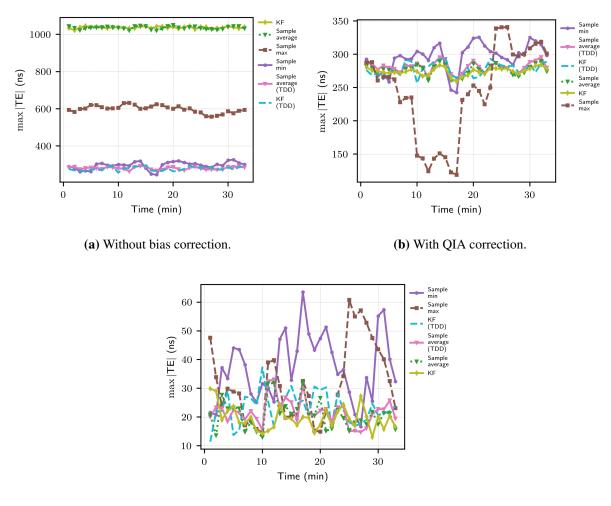

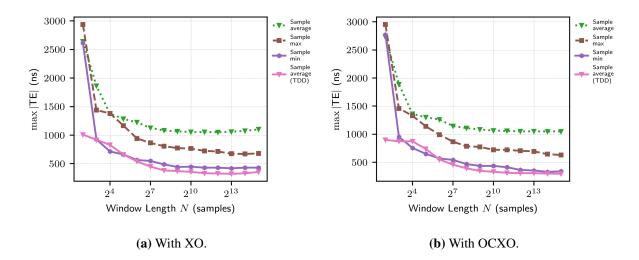

| maximum absolute time error $(max TE )$ results from the experiments with four |               |

|--------------------------------------------------------------------------------|---------------|

| physical hops.                                                                 | 79            |

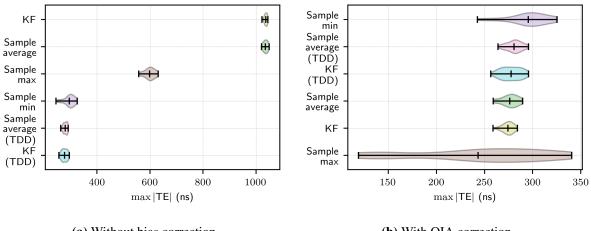

| max TE  results from the experiment with four physical hops and XO oscillator. | 81            |

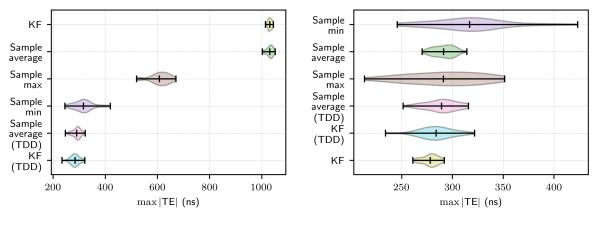

| max TE  violin plots from the experiment with four physical hops and XO os-    |               |

| cillator.                                                                      | 83            |

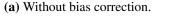

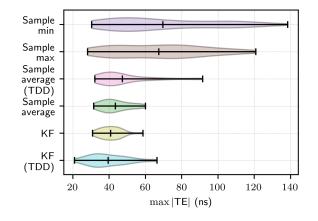

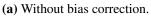

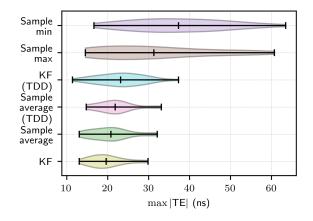

| max TE  results from the experiment with four physical hops and OCXO oscil-    |               |

| lator                                                                          | 85            |

| max TE  violin plots from the experiment with four physical hops and OCXO      |               |

| oscillator.                                                                    | 86            |

| Cumulative drift estimation error on the experiment with four physical hops    | 87            |

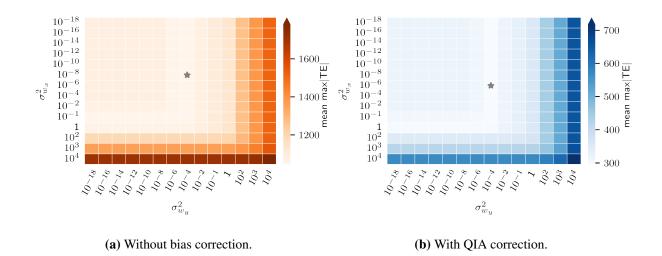

| max TE  in terms of window length using four physical hops and without bias    |               |

| correction                                                                     | 88            |

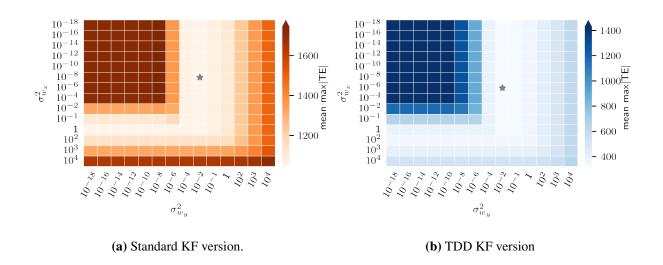

| Heatmap from KF Q matrix tunning using four physical hops and the XO oscil-    |               |

| lator                                                                          | 89            |

| Heatmap from KF Q matrix tunning using four physical hops and the OCXO         |               |

| oscillator.                                                                    | 89            |

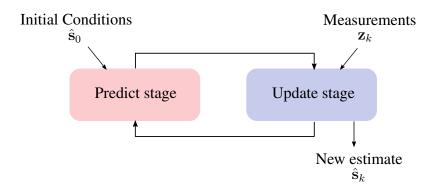

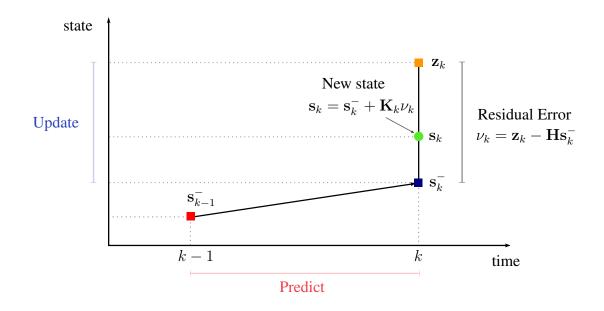

| Predict and update stages from Kalman filtering                                | 96            |

| Pictorial representation of Kalman filtering process.                          | 98            |

|                                                                                | physical hops |

# **List of Tables**

| 2.1 | Main sources of delay.                                                        | 20 |

|-----|-------------------------------------------------------------------------------|----|

| 4.1 | PTP-Unaware switches used in the testbed.                                     | 47 |

| 5.1 | Transmission delay considering a PTP frame with 80 bytes and a GbE interface. | 63 |

| 5.2 | Average delays from switch #1 using port-based VLAN                           | 63 |

| 5.3 | Average delays from switch #2 using port-based virtual local area network     |    |

|     | (VLAN)                                                                        | 64 |

| 5.4 | Delays using multiples physical switches.                                     | 65 |

| 5.5 | Ideal delay asymmetry from the experiment with XO oscillator calculated by    |    |

|     | PTP-DAL                                                                       | 81 |

| 5.6 | Static delay asymmetry from good packets from the experiment with the XO      |    |

|     | oscillator.                                                                   | 81 |

| 5.7 | Ideal delay asymmetry from the experiment with OCXO oscillator                | 84 |

| 5.8 | Static delay asymmetry from good packets from the experiment with OCXO        |    |

|     | oscillator.                                                                   | 85 |

# Contents

| Ac | know    | ledgme        | nt                                                   |       |   |   | vi    |

|----|---------|---------------|------------------------------------------------------|-------|---|---|-------|

| Gl | ossar   | У             |                                                      |       |   |   | vii   |

| Sy | mbol    | 5             |                                                      |       |   |   | xi    |

| Li | st of I | Figures       |                                                      |       |   |   | xvi   |

| Li | st of ] | <b>Fables</b> |                                                      |       |   |   | xix   |

| Co | ontent  | ts            |                                                      |       |   |   | XX    |

| Ał | ostrac  | t             |                                                      |       |   | 2 | xxiii |

| Re | esumo   | )             |                                                      |       |   | 2 | xxiv  |

| 1  | Intro   | oductio       | n                                                    |       |   |   | 1     |

|    | 1.1     | Motiva        | tion                                                 | <br>• | • |   | 2     |

|    | 1.2     | Outline       | 2                                                    | <br>• | • |   | 5     |

|    | 1.3     | Contri        | butions                                              | <br>• |   |   | 6     |

|    | 1.4     | Publica       | ations                                               | <br>• | • |   | 6     |

| 2  | Fun     | dament        | als of Time Synchronization in Packet-based Networks |       |   |   | 7     |

|    | 2.1     | Synch         | conization Basics                                    | <br>• |   |   | 7     |

|    |         | 2.1.1         | Types of Synchronization: Frequency, Phase and Time  |       |   |   | 8     |

|    |         | 2.1.2         | Clock Basics                                         | <br>• | • |   | 9     |

|    |         | 2.1.3         | Measurements of Time Error                           |       |   |   | 12    |

|    | 2.2     | IEEE 1        | 588 Precision Time Protocol (PTP)                    |       |   |   | 13    |

|    |         | 2.2.1         | PTP Timing-exchange Mechanisms                       |       |   |   | 14    |

|   |         | 2.2.2 Sources of Delay Asymmetry          | 17 |  |  |

|---|---------|-------------------------------------------|----|--|--|

| 3 | Sync    | chronization in TDD Fronthaul             | 21 |  |  |

|   | 3.1     | Overview                                  | 21 |  |  |

|   | 3.2     | PTP Classification Based on TDD cycle     | 24 |  |  |

|   |         | 3.2.1 PTP Cycle Location                  | 25 |  |  |

|   |         | 3.2.2 K-means based Classifier            | 28 |  |  |

|   | 3.3     | Time and Frequency Offset Estimators      | 31 |  |  |

|   |         | 3.3.1 Related Work                        | 31 |  |  |

|   |         | 3.3.2 Kalman Filtering                    | 34 |  |  |

|   |         | 3.3.3 Packet Filtering                    | 38 |  |  |

|   |         | 3.3.4 Time Offset Drift Estimation        | 40 |  |  |

|   | 3.4     | Delay Asymmetry Estimation                | 40 |  |  |

|   |         | 3.4.1 Related work                        | 41 |  |  |

|   |         | 3.4.2 Queuing-Induced PTP Delay Asymmetry | 41 |  |  |

| 4 | Testbed |                                           |    |  |  |

|   | 4.1     | Testbed Overview                          | 46 |  |  |

|   | 4.2     | PTP Infrastructure                        | 49 |  |  |

|   | 4.3     | Fronthaul Traffic                         | 50 |  |  |

|   | 4.4     | TDD FH Implementation                     | 51 |  |  |

|   | 4.5     | Acquisition of Labeled Datasets           | 55 |  |  |

|   | 4.6     | PTP-DAL                                   | 56 |  |  |

| 5 | Resi    | llts                                      | 59 |  |  |

|   | 5.1     | Experimental Setup                        | 59 |  |  |

|   | 5.2     | Delay Analysis                            | 61 |  |  |

|   |         | 5.2.1 PTP without FH Traffic              | 61 |  |  |

|   |         | 5.2.2 PTP with FH Traffic                 | 65 |  |  |

|   | 5.3     | TDD Packet Classifier Experiments         | 69 |  |  |

|   |         | 5.3.1 PTP Cycle location                  | 70 |  |  |

|   |         | 5.3.2 K-means Based Classifier            | 72 |  |  |

|   | 5.4     | Queuing Induced Asymmetry Experiments     | 76 |  |  |

|   | 5.5     | Synchronization for TDD FH Experiments    | 80 |  |  |

xxi

| 6   | Conclusion and Future Work |                            | 91 |  |

|-----|----------------------------|----------------------------|----|--|

|     | 6.1                        | Conclusion                 | 91 |  |

|     | 6.2                        | Future Work                | 93 |  |

| A   | Discrete Kalman Filter     |                            | 94 |  |

|     | A.1                        | State-space Representation | 94 |  |

|     | A.2                        | Prediction Stage           | 96 |  |

|     | A.3                        | Update Stage               | 97 |  |

| Bił | Bibliography 10            |                            |    |  |

xxii

#### Abstract

In fifth-generation (5G) mobile communications, clock synchronization is essential for the correct operation of the network. In this context, as 5G networks are moving to packetbased networks, the IEEE 1588 precision time protocol (PTP) is the industry-accepted protocol for flexibly distributing time synchronization. However, when PTP packets are transported in a cost-effective network without specialized equipment, two main issues impact the performance of PTP: packet delay variation (PDV) and delay asymmetries. In this type of network, the use of algorithms to filter the errors introduced by PDV and delay asymmetry is usually helpful. Thus, this work aims to present an analysis of PTP performance on a cost-effective network when time-division duplex (TDD) is used on the radio interface. We propose new algorithms to improve the PTP performance that take advantage of the fronthaul (FH) periodic utilization pattern when using TDD on the radio interface. Our evaluation is carried out on a realistic testbed composed of field-programmable gate arrays (FPGAs). The results indicate that the PTP performance can be improved on this type of network by using the knowledge about the FH periodicity to correct the queuing-induced asymmetry and more effectively filter the PDV.

#### Resumo

Em redes móveis de quinta geração (5G), a sincronização do relógio é essencial para o correto funcionamento da rede. Nesse contexto, à medida que as redes 5G estão migrando para redes baseadas em pacotes, o protocolo de tempo de precisão IEEE 1588 (PTP) é o protocolo aceito pela industria para distribuição flexível de sincronização de tempo. No entanto, quando os pacotes PTP são transportados em uma rede mais econômica, sem equipamento especializado, dois problemas principais afetam o desempenho do PTP: variação de atraso de pacotes (PDV) e assimetrias de atraso. Nesse tipo de rede, o uso de algoritmos para filtrar os erros introduzidos por PDV e assimetria de atraso costuma ser útil. Assim, este trabalho tem como objetivo apresentar uma análise do desempenho do PTP em uma rede econômica quando duplex por divisão de tempo (TDD) é usado na interface de rádio. Este trabalho propõe novos algoritmos para melhorar o desempenho do PTP que aproveitam o padrão de utilização periódica do fronthaul (FH) ao usar TDD na interface de rádio. Nossa avaliação é realizada em um ambiente de teste realista composto de arranjos de porta programável em campo (FPGAs). Os resultados indicam que o desempenho do PTP pode ser melhorado neste tipo de rede usando o conhecimento sobre a periodicidade do FH para corrigir a assimetria induzida pelo enfileiramento e filtrar o PDV de forma mais eficaz.

## Chapter 1

## Introduction

The synchronization of clocks in distributed systems has been an important long-standing problem. It enables applications to operate using the same notion of time, which enables key functions like determining the order of transactions in a financial application. Synchronization is a fundamental building block in different fields such as wireless communication, industrial automation [3], Internet of things (IoT) [4], financial applications [5] and many more [6, 7]. However, synchronizing two or more clocks is typically challenging due to many different aspects. One of them is that each clock tends to drift differently due to inherent instabilities and environmental factors such as temperature [8].

In mobile networks, time synchronization became crucial in the fourth-generation (4G) and fifth-generation (5G) networks. For instance, the frequency accuracy requirement within  $\pm 50$  parts ber bilion (ppb), needed for basic operations on base station (BS), has not changed in the recent mobile generations [9, Chapter 7]. For example, BS needs accurate frequency to transmit in the correct radio frequency (RF) spectrum and to support handover operation. In contrast, time synchronization becomes more important with the advance of cooperative transmission technologies in recent generations. For instance, 5G mostly rely on time-division duplex (TDD) technology [10], which requires time synchronization of the BS within  $\pm 1.5\mu$ s absolute time error [11].

In the majority of mobile network deployments, the primary method of synchronizing the clocks of distributed network devices was through the utilization of global navigation satellite systems (GNSS). However, the implementation of 5G mobile networks introduced several demands, such as the enhancement of cell density, indoor cell coverage, and deployment capabilities in areas that present geographical challenges such as tunnels, buildings, and factories where satellite visibility is limited. As a consequence, the use of GNSS-based synchronization in these scenarios becomes difficult as the GNSS receiver must have a line of sight to the satellites. Thus, new techniques are being explored to meet the stringent time synchronization required by 5G networks and reduce deployment costs.

The industry is adopting a combination of GNSS and IEEE 1588 precision time protocol (PTP) [12]. Rather than deploying GNSS everywhere, these networks are increasingly using the IEEE 1588 packet-based network synchronization, where GNSS still provide the primary timing reference and PTP is responsible for distributing the time synchronization among the network devices. PTP enables synchronization by exchanging time information over packet-based networks between highly accurate devices, called master clocks, and multiple less accurate clocks, called slave clocks. The performance heavily depends on the networks that are being used to transmit the PTP packets. For example, in PTP-unaware networks, the PTP performance can be very affected depending on the nature of the network traffic being transmitted together with PTP, which can lead to high packet delay variation (PDV) and delay asymmetry. As clarified in the sequel, this work will focus on this scenario as this type of network, if properly designed, can be used to provide accurate synchronization in a very cost-effective manner.

In the remainder of this chapter, Section 1.1 describes the context and motivation for this work, presenting an overview of the use of PTP in timing-unaware networks and how the information about the nature of the traffic can benefit the synchronization performance in this scenario. Next, Section 1.2 outlines the content presented in the chapters of this work. Finally, Section 1.3 summarizes the research contributions.

### 1.1 Motivation

Mobile networks always required some kind of synchronization. Most legacy networks utilized frequency-division duplex (FDD) as the technique to separate the downlink and uplink channels. In FDD, both the uplink and downlink radios transmit simultaneously but at different frequencies. A predetermined offset is used to separate these frequencies and avoid any interference. As a consequence, when using FDD, frequency synchronization is necessary at the radio interface. This requirement for synchronization is necessary for many reasons. For example, as the local oscillator at the radio equipment is utilized as the source for the frequency being transmitted by the radio on the air, any deviation in the frequency of the local oscillator results in the radio transmitting at an incorrect frequency. Therefore, one of the reasons for frequency synchronization is to ensure that the radios transmit at the correct RF.

Traditionally, frequency synchronization was delivered to the network nodes using timedivision multiplexing (TDM) networks, which were naturally synchronous. For example, in 4G cloud radio access network (C-RAN), the fronthaul (FH) network was based on a point-topoint synchronous network using technology like common public radio interface (CPRI) [13]. However, motivated by the flexibility and cost-effectiveness of the Ethernet technology and to meet the demands of ever-growing bandwidth, the industry started to move the radio access networks (RAN) and the core network to packet-based networks. The problem is that, unlike CPRI that has frequency synchronization built-in, packet-based technologies like Ethernet are asynchronous and require other means for distributing synchronization.

Additionally, mobile networks also support technologies like TDD. In TDD mode, networks optimize spectral efficiency by sharing the same frequency for uplink and downlink radio, but at different time slots. As a consequence, TDD requires accurate time synchronization due to the time-sensitive nature of TDD operation. For example, to avoid unwanted interference between neighboring base stations and user equipment. In the case of more complex networks, even tighter time synchronization is required to enable more advanced technologies such as carrier aggregation (CA), distributed multiple-input multiple-output (MIMO) and coordinated multi-point (CoMP) [14, Chapter 6]. Therefore, a crucial requirement for deploying the recent generations of mobile networks in a packet-based network is the ability to provide highly accurate clock synchronization.

The most common method for achieving time synchronization is through GNSS. The GNSS receiver located within the BS synchronizes with the atomic clocks present in satellites, thereby providing a reliable and highly accurate synchronization. However, when it comes to 5G networks, several challenges must be addressed. For instance, the GNSS antenna must have a line of sight (LOS) to the satellites, which becomes increasingly difficult in dense urban areas and infeasible in indoor environments. Additionally, as the industry shifts towards the use of smaller, more densely distributed BS in 5G networks, the cost of installing GNSS equipment at all RAN sites becomes impractical. Besides, providing synchronization only using GNSS becomes problematic due to security issues such as *jamming*, where the GNSS signal is completely blocked and *spoofing*, where the GNSS signal is replaced by a similar signal but incorrect one [15]. Hence, as time synchronization becomes more important in telecommunication

networks, the need for distributing synchronization using packet networks becomes necessary.

In this context, the PTP is the industry-accepted protocol to distribute time synchronization in a packet network in a highly scalable way. However, one major issue is that the timing messages traveling between the master and slave node can encounter several intermediate switches and routers, accumulating random delays at each node. This randomness in the synchronization path is called PDV and affects the synchronization performance. Additionally, the PTP performance is also affected when the packet delay in the forward and reverse directions are unequal, known as delay asymmetry. The problem is that Ethernet was not designed to guarantee end-to-end latency. Thus, to achieve high synchronization accuracy, ITU-T has defined a full-timing support (FTS) [16] network to be used between the master and slave clocks.

In a FTS network, also known as PTP-aware network, all the networks elements are composed by boundary clock (BC) and transparent clock (TC) [17]. The BC and TC are specialized switches or routers that provide the functionality to mitigate the PDV and delay asymmetry that the PTP packets suffer when traversing the network. For instance, TC nodes are specialized nodes that can measure and compensate for the time taken for the PTP packet to pass through the device to alleviate the PDV. Hence, FTS networks provide a more reliable and accurate synchronization. However, it is more expensive.

Synchronizing clocks in a timing-unaware network, i.e., without using FTS networks, is a more complex challenge. This type of network is composed of PTP-unaware network elements, switches and routers that do not provide any specialized functionality for PTP. This common case is referred to as partial-timing support (PTS) [18]. The presence of PTP-unaware devices impacts synchronization performance due to the high PDV, caused by variable queuing delays over the network, and delay asymmetries. However, this scenario offers flexibility and cost-effectiveness. In this type of network, there is no need to use specialized equipment on the transport network, so network operators could use cheaper equipment or even already deployed networks without the need to make hardware modifications to accommodate PTP-based synchronization. In PTS networks, PTP can also be used as a second source of timing to backup GNSS, which is defined as assisted partial-timing support (APTS) [18].

In this context, the objective of this work is to present a detailed analysis of PTP performance in a cost-effective PTP-unaware network when TDD is being used to coordinate the transmission and reception of data on the radio interface. In this type of network, the FH network exhibits a periodic utilization pattern due to the use of TDD system on the radio interface. By taking advantage of the periodic nature of the FH traffic, the PTP performance can be improved. This idea was proposed by our partners at Ericsson in [2]. Thus, this works focus on extending and validating the ideas presented in [2]. To this end, this work uses a testbed based on field-programmable gate arrays (FPGAs) to provide a realistic analysis of how the FH periodic traffic affects PTP and also proposes new techniques to improve the synchronization performance by using the information about the TDD pattern to mitigate PDV and the asymmetry introduced by queuing delay using specialized algorithms.

### 1.2 Outline

This work is organized as follows:

- Chapter 2 provides the fundamental concepts used by this work. It presents some definitions regarding clocks, the noises that affect their accuracies and stability, and the metrics used for their characterization. It also describes the IEEE 1588 protocol, including a compact review of the noises that affect its performance. Lastly, it presents a discussion about the source of delay asymmetries that affects PTP.

- Chapter 3 discusses the key ideas about using the information about the periodicity from the FH traffic when using TDD on the radio interface to improve the PTP synchronization performance in a timing-unaware network. Additionally, the chapter presents a literature review of different synchronization algorithms. In particular, it presents different strategies to estimate the time and frequency offset. Moreover, Chapter 3 discusses a new method for estimating the bias induced by the queuing delay in such networks.

- Chapter 4 presents a brief description of the testbed used in this work. More specifically, the changes introduced to make a more realistic analysis in a FH that presents a periodic pattern. It also discusses how the datasets are acquired and how the evaluation is carried out using a processing tool called PTP dataset analysis library (PTP-DAL).

- Chapter 5 presents the experimental results using the datasets acquired from the testbed. It starts by presenting an analysis of the PTP delay distribution observed on the datasets used in this work. It also includes the analysis of two types of hop configurations: VLANbased hops using one switch and multiple physical switches. It also describes the results

achieved by the methods used to classify the PTP packets based on the FH traffic. Furthermore, it includes a discussion about the results achieved by the proposed method for estimating the bias induced by queuing delay. Finally, it presents the achieved synchronization performance with different algorithms and oscillators.

• Lastly, Chapter 6 presents a summary of the results present in this work and provides directions for future work.

## **1.3** Contributions

The contributions of this work are:

- The analysis of PTP performance in a PTP-unaware network that presents periodic traffic using different types of synchronization algorithms such as Kalman filter (KF), sample minimum, maximum and average.

- The adaptations proposed to the KF and sample average algorithms to use the knowledge of the good and bad packets to improve the synchronization performance.

- The proposal of a new method to classify PTP packets using a K-means based classifier.

- The proposal of a new method to estimate the queuing-induced delay asymmetry in a network that presents periodic traffic.

- Discussion about delay distribution present in FH networks, such as the processing delay produced by different switches and the impact of these delays on the performance of PTP.

- A hardware-based evaluation of the impact of periodic FH traffic on the PTP performance.

### **1.4 Publications**

The work in [19] was produced as an initial effort to understand the use of KF for the specific problem of clock synchronization. More specifically, the work focuses on how the clock model, in conjunction with the measurements provided by the PTP algorithm, can be expressed in the Kalman Filter form. It also presents the KF performance using a legacy Ethernet network with different network loads and two different oscillators.

## Chapter 2

# Fundamentals of Time Synchronization in Packet-based Networks

This chapter introduces the fundamental concepts used in this work and is divided into two major sections. In Section 2.1, the basic concepts related to clock synchronization are presented. For example, the different types of synchronization, how a clock device can be modeled mathematically, and which metrics are used for performance characterization. Next, Section 2.2 describes how the IEEE 1588 technology works.

## 2.1 Synchronization Basics

Maintaining many devices synchronized is a very important task in many applications. Generally, these applications need to have some kind of synchronization for various devices at different geospatial locations to perform some type of coordinated task. These devices usually perform timekeeping locally using a clock. The clock can be defined as a device composed of an oscillator and a counter. The oscillator is a device that produces a periodic electric signal called *clock signal*, and the counter is responsible for keeping track of the oscillator's cycles to keep track of the elapsed time.

However, these timekeeping techniques are subject to errors that can accumulate over time due to the imperfection of the clock frequency generated by the oscillators. The clock frequency varies mainly with power, aging, and temperature [8]. Therefore, two similar oscillators are not guaranteed to oscillate with identical frequency. The magnitude of such errors depends on the oscillator's precision and stability, and most of the time the quality of such devices is

proportional to their prices. As a result, it becomes almost impossible to maintain any kind of synchronization between many devices only using the local clock without using any additional technique. Thus, there are many methods for providing synchronization to various devices across a distributed network without depending only on the local time clock.

#### 2.1.1 Types of Synchronization: Frequency, Phase and Time

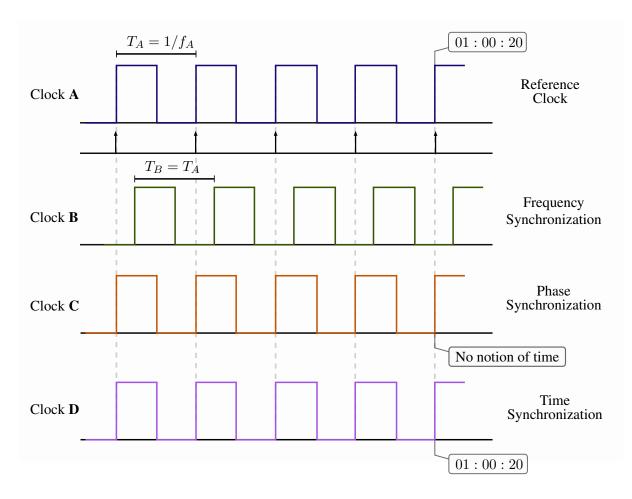

The word synchronization has multiple meanings. It can be mainly classified as frequency, phase or time synchronization. Thus, it is essential to distinguish these different types of alignment. Fig. 2.1 highlights the differences. The specific definitions presented below are based on the ITU-T Recommendations G.8260 [20] and G.810 [21].

Figure 2.1: Frequency, phase, and time synchronization.

The frequency synchronization is related to the alignment of clocks in frequency. It means that the significant instants, for example, the rising edges of different clocks, occur at the same

rate. In other words, they have the same number of pulses within the same period. This type of alignment is also referred to as *syntonization*.

Another type of synchronization is the so-called phase synchronization. When two or more clocks are said to be synchronized in phase, it means that significant events occur at the same instant. Note that, if the rising edge of two clocks occurs at the same instant, it also follows that they occur at the same rate. Therefore, phase synchronization implies syntonization.

Finally, time synchronization is closely related to phase synchronization. In this type of alignment, the clocks are synchronized in phase, and they also share a common time scale, e.g., each period of the reference time is marked and dated. Thus, the devices should share the same absolute time of day (ToD). For this type of synchronization, the devices should be equipped with a real-time clock (RTC), which is a module responsible for keeping track of the ToD.

Note that time synchronization implies phase synchronization, and phase synchronization implies frequency synchronization. Therefore, distributing time synchronization among different devices is one way to achieve both frequency and phase synchronization. This is the idea of the widely used IEEE 1588 protocol, which will be discussed later in this chapter.

#### 2.1.2 Clock Basics

In the synchronization field, the word clock is most used to refer to a device that is capable of measuring time, i.e., an RTC. It is usually composed of an oscillator and a time counter. The oscillator is a device that produces a periodic electric signal, referred to as *clock signal*, which drives the time counter. The counter is responsible for keeping track of the oscillator cycles that have occurred, to keep track of the elapsed time. For example, if an RTC is driven by a clock signal that has a nominal frequency  $f_{nom} = 100$  MHz, at each rising edge the RTC would increment  $1/f_{nom} = 10$  ns. Thus, after  $f_{nom} \times (1/f_{nom})$  the RTC would accumulate a realworld second. Additionally, an RTC usually holds ToD information in a specific time standard, such as coordinated universal time (UTC) or international atomic time (TAI).

If a clock is ideal, it has a perfect frequency, which would yield a perfect measurement of the elapsed time. However, in practice, the clock is not ideal. That means the clock frequency that drives the counter is not perfect. Due to the random phase and frequency fluctuations that affect any oscillator. Hence, the time counter is strongly disturbed over time by the oscillator's deviation, which is caused by many factors such as temperature and aging effects [8].

The periodic signal produced by an oscillator could be modeled as a pure sinusoidal wave

if the clock was ideal. However, any real device is disturbed by unavoidable random noises, such as drifts due to frequency instability or environmental effects. Hence, many studies discuss a tractable mathematical model for the output of an oscillator. In the literature [22–24], a commonly adopted model is the quasi-sinusoidal voltage, mathematically represented by:

$$V(t) = V_0 \sin \Phi(t), \tag{2.1}$$

where  $V_0$  is the amplitude that, for simplicity, is assumed to be constant,  $f_{nom}$  is the nominal frequency and  $\Phi(t)$  is the total instantaneous phase, which is measured in radians. More specifically, the total instantaneous phase  $\Phi(t)$  can be given as follows:

$$\Phi(t) = 2\pi f_{nom}t + \phi(t), \qquad (2.2)$$

where  $\phi(t)$  is the so-called random phase deviation. The term  $\phi(t)$  is a random process that models all the random deviations with respect to the nominal frequency  $f_{nom}$  [22].

In this model, the random phase deviation  $\phi(t)$  is typically the primary concern when dealing with oscillators. The phenomenon is well understood by the literature, and there are several analytical techniques for its characterization. In the sequel, we discuss some very useful measures used in the literature.

First, it is interesting to note that the timing information of the signal V(t) is carried by its total instantaneous phase  $\Phi(t)$ . Additionally, recall that the definition of instantaneous angular frequency is the rate of change of phase, as follows:

$$\omega(t) = 2\pi f(t) = \frac{\mathrm{d}\Phi(t)}{\mathrm{d}t},\tag{2.3}$$

where  $\omega(t)$  is the instantaneous angular frequency given in radians per second and f(t) is the instantaneous frequency given in hertz. Thus, assuming (2.3) and (2.2), the *instantaneous frequency* can be expressed as defined in [25]:

$$f(t) = \frac{1}{2\pi} \frac{\mathrm{d}\Phi(t)}{\mathrm{d}t}$$

$$= f_{nom} + \frac{1}{2\pi} \frac{\mathrm{d}\phi(t)}{\mathrm{d}t}, \qquad (2.4)$$

where the second term on the right-hand side represents the instantaneous frequency fluctuation. In other words, it is the rate of phase change over time.

One should note that oscillators can only be characterized by measuring them against a reference oscillator. Thus, a useful definition is the so-called *fractional*, or *normalized frequency*

offset defined as:

$$y(t) = \frac{f(t) - f_{nom}}{f_{nom}},\tag{2.5}$$

which is the instantaneous frequency fluctuation normalized to the nominal frequency. This quantity is dimensionless and is generally given in terms of parts per million (ppm) or parts per billion (ppb). The normalized frequency offset can also be interpreted in a more general way, where the  $f_{nom}$  is defined as the frequency of the reference clock oscillator.

Another important metric is the time offset x(t), which is the difference between the local time and the reference (ideal) time, defined as follows:

$$x(t) = T(t) - t,$$

(2.6)

where T(t) is the local time measured by the clock at the "true" instant t. Mathematically, the time function T(t) is defined as:

$$T(t) = \frac{\Phi(t)}{2\pi f_{nom}} = t + \frac{\phi(t)}{2\pi f_{nom}}.$$

(2.7)

Thus, by substituting (2.7) in (2.6), the time offset can be interpreted as the random phase deviation converted into time and measured in seconds. Another way to calculate the time offset is by assuming (2.4) and integrating (2.5).

Note that the true instantaneous frequency f(t) is impossible to be measured since it will always involve some sample time, e.g., a window of time from which the oscillator is observed. Therefore, we can define an *average fractional frequency* over a period  $\Delta t$  as:

$$y(t) = \frac{x(t + \Delta t) - x(t)}{\Delta t},$$

(2.8)